# Transceiver Group

Never stop thinking.

Edition 1997-07-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 3/1/00. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# PEB 2265

Two Channel Codec Filter with IOM-2 Interface

Never stop thinking.

| PEB 2265<br>Preliminary<br>Revision History: |          | <b>1997-07-01</b> DS 1             |  |  |

|----------------------------------------------|----------|------------------------------------|--|--|

| Previous V                                   | /ersion: | 01.96                              |  |  |

| Page                                         | Subjects | major changes since last revision) |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

|                                              |          |                                    |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table o | of Contents Pa                                                  | age |

|---------|-----------------------------------------------------------------|-----|

| 1       | Overview                                                        | 10  |

| 1.1     | Pin Configuration (top view)                                    | 12  |

| 1.2     | Pin Definition and Functions                                    | 13  |

| 1.2.1   | Common Pins for all Channels                                    | 13  |

| 1.2.2   | Specific Pins for Channel 1                                     | 14  |

| 1.2.3   | Specific Pins for Channel 2                                     | 15  |

| 1.3     | IOM-2 SICOFI-2 Principles                                       |     |

| 1.4     | IOM-2 SICOFI-2 Signal Flow Graph (for either channel)           | 17  |

| 1.4.1   | Transmit Path                                                   |     |

| 1.4.2   | Receive Path                                                    | 18  |

| 1.4.3   | Loops                                                           | 18  |

| 1.4.4   | Test Features                                                   | 18  |

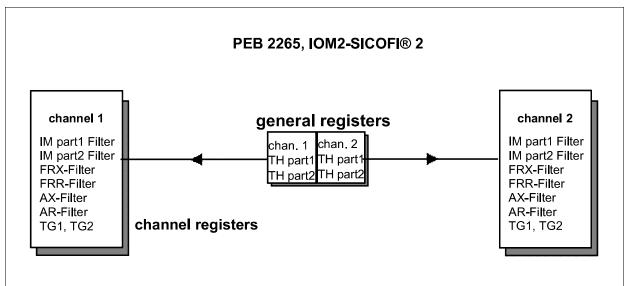

| 1.5     | IOM-2 SICOFI-2 Block Diagram                                    | 19  |

| 1.6     | IOM®-2 Interface                                                | 20  |

| 1.6.1   | IOM®-2 Interface Timing for 16 voice channels (per 8 kHz frame) |     |

| 1.6.2   | IOM®-2 Interface Timing                                         |     |

| 1.6.3   | IOM®-2 Interface Timing                                         |     |

| 1.6.4   | IOM <sup>®</sup> -2 Time Slot Selection                         |     |

| 2       | Programming the IOM-2 SICOFI-2                                  | 25  |

| 2.1     | Types of Monitor Bytes                                          |     |

| 2.2     | IOM-2 SICOFI-2 Commands                                         |     |

| 2.2.1   | SOP - Write Commands                                            | 27  |

| 2.2.2   | XOP - Write Commands                                            | 28  |

| 2.2.3   | COP - Write Commands                                            | 29  |

| 2.2.4   | SOP - Read Commands                                             | 30  |

| 2.2.5   | XOP - Read Commands                                             | 31  |

| 2.2.6   | COP - Read Commands                                             | 32  |

| 2.2.7   | Example for a Mixed Command                                     | 32  |

| 2.3     | SOP Command                                                     | 34  |

| 2.3.1   | CR1 Configuration Register 1                                    | 35  |

| 2.3.2   | CR2 Configuration Register 2                                    | 36  |

| 2.3.3   | CR3 Configuration Register 3                                    |     |

| 2.3.4   | CR4 Configuration Register 4                                    | 39  |

| 2.4     | COP Command                                                     | 40  |

| 2.5     | XOP Command                                                     | 42  |

| 2.5.1   | XR1 Extended Register                                           | 42  |

| 2.5.2   | XR2 Extended Register 2                                         |     |

| 2.5.3   | XR3 Extended Register 3                                         |     |

| 2.5.4   | XR4 Extended Register 4                                         |     |

| 2.6     | SLIC Interface                                                  |     |

| 2.7     | IOM®-2 Interface Command/Indication Byte                        |     |

| 2.8     | Operating Modes                                                 |     |

|         | •                                                               |     |

| 2.8.1 | RESET (Basic setting mode)                                     |    |

|-------|----------------------------------------------------------------|----|

| 2.8.2 | Standby Mode                                                   |    |

| 2.8.3 | Operating Mode                                                 |    |

| 2.9   | Programmable Filters                                           |    |

| 2.9.1 | Impedance Matching Filter                                      |    |

| 2.9.2 | Transhybrid Balancing (TH) Filter                              |    |

| 2.9.3 | Filters for Frequency Response Correction                      | 51 |

| 2.9.4 | Amplification/Attenuation -Filters AX1, AX2, AR1, AR2          |    |

| 2.9.5 | Amplification/Attenuation Receive (AR1, AR2)-Filter            |    |

| 2.9.6 | Amplification/Attenuation Transmit (AX1, AX2)-Filter           | 52 |

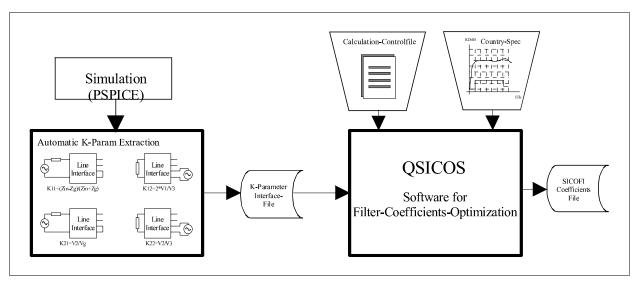

| 3     | QSICOS Software                                                |    |

| 3.1   | QSICOS Supports                                                | 54 |

| 4     | Transmission Characteristics                                   |    |

| 4.1   | Frequency Response                                             |    |

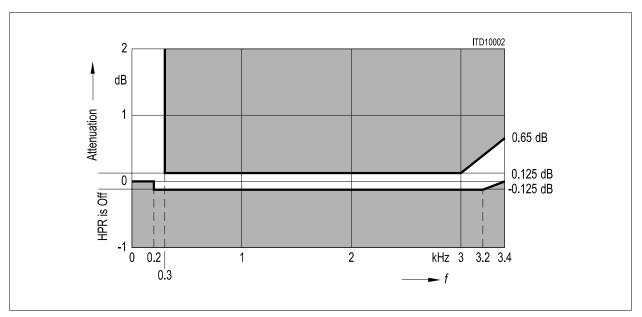

| 4.1.1 | Receive: reference frequency 1 kHz, input signal level 0 dBm0  |    |

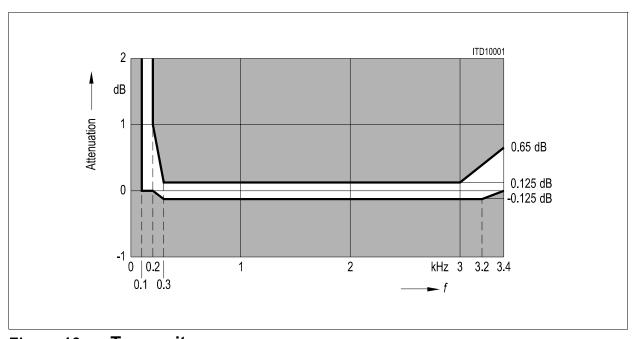

| 4.1.2 | Transmit: reference frequency 1 kHz, input signal level 0 dBm0 |    |

| 4.2   | Group Delay                                                    |    |

| 4.2.1 | Group Delay absolute values: Input signal level 0 dBm0         |    |

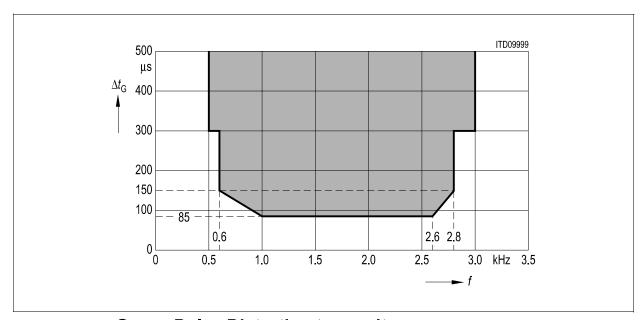

| 4.2.2 | Group Delay Distortion transmit: Input signal level 0 dBm0     |    |

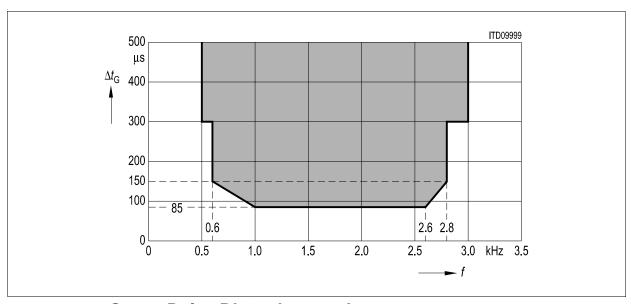

| 4.2.3 | Group Delay Distortion receive: Input signal level 0dBm0       | 59 |

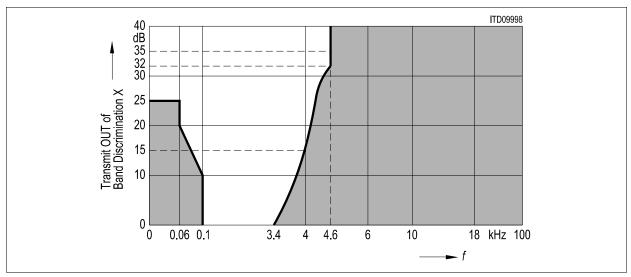

| 4.3   | Out-of-Band Signals at Analog Input                            | 60 |

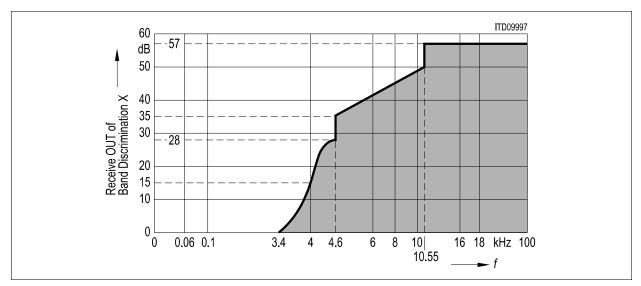

| 4.4   | Out-of-Band Signals at Analog Output                           |    |

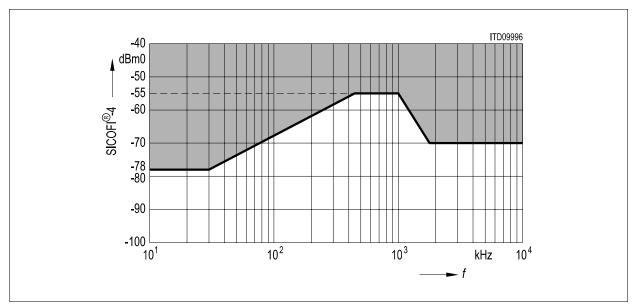

| 4.5   | Out of Band Idle Channel Noise at Analog Output                | 62 |

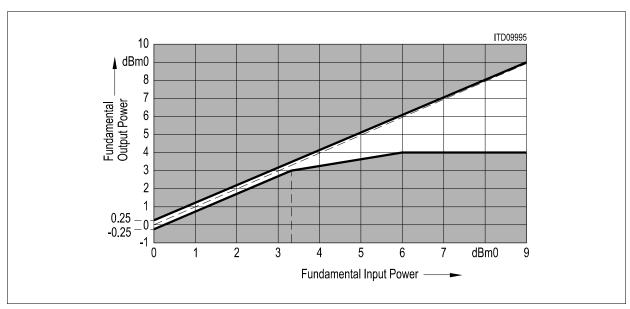

| 4.6   | Overload Compression                                           | 63 |

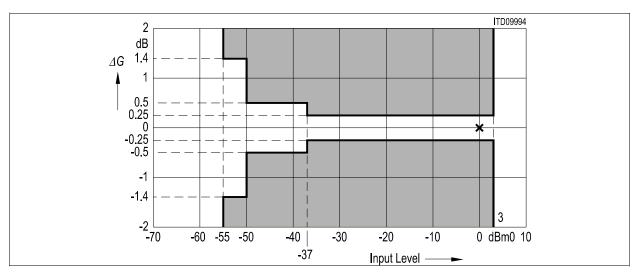

| 4.7   | Gain Tracking (receive or transmit)                            | 64 |

| 4.8   | Total Distortion                                               | 65 |

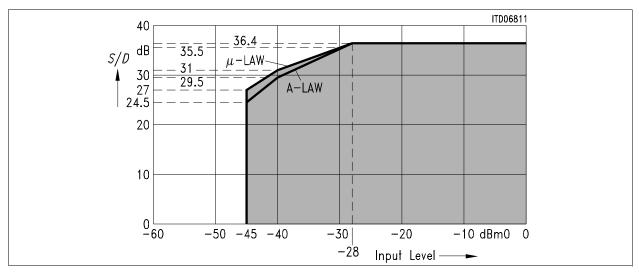

| 4.8.1 | Total Distortion Measured with Sine Wave                       | 65 |

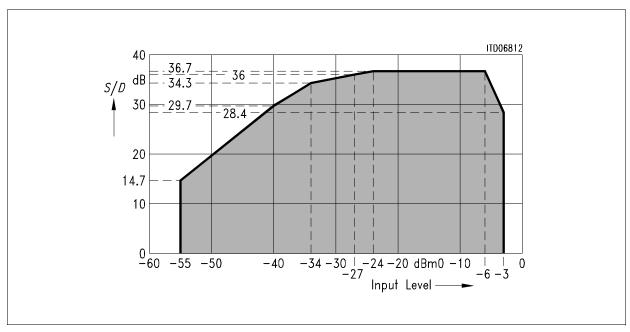

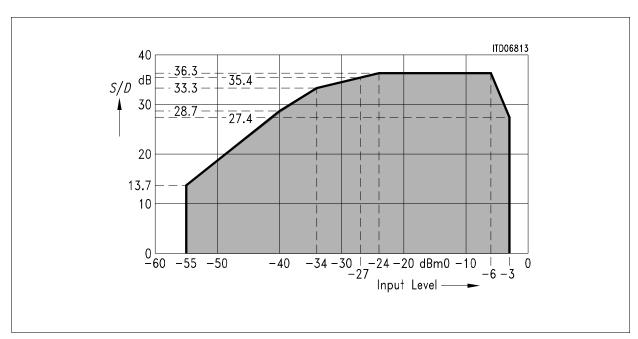

| 4.8.2 | Total Distortion Measured with Noise According to CCITT        | 66 |

| 4.9   | Single Frequency Distortion                                    | 67 |

| 4.10  | Transhybrid Loss                                               | 67 |

| 5     | Electrical Characteristics                                     |    |

| 5.1   | Absolute Maximum Ratings                                       |    |

| 5.2   | Operating Range                                                | 69 |

| 5.3   | Digital Interface                                              | 70 |

| 5.4   | Analog Interface                                               | 71 |

| 5.5   | RESET Timing                                                   | 71 |

| 5.6   | IOM®-2 Interface Timing                                        | 72 |

| 5.6.1 | 4-MHz Operation Mode (Mode = 1)                                | 72 |

| 5.6.2 | 2-MHz Operation Mode (Mode = 0)                                | 73 |

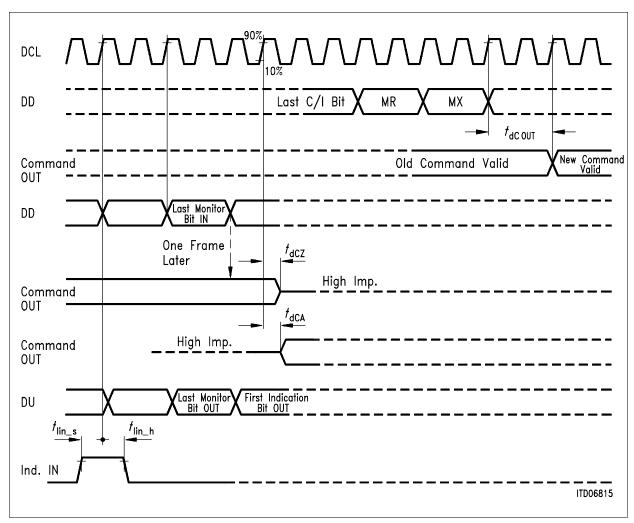

| 5.7   | IOM®-2 Command/Indication Interface Timing                     |    |

| 5.7.1 | 4-MHz Operation Mode (Mode = 1)                                | 74 |

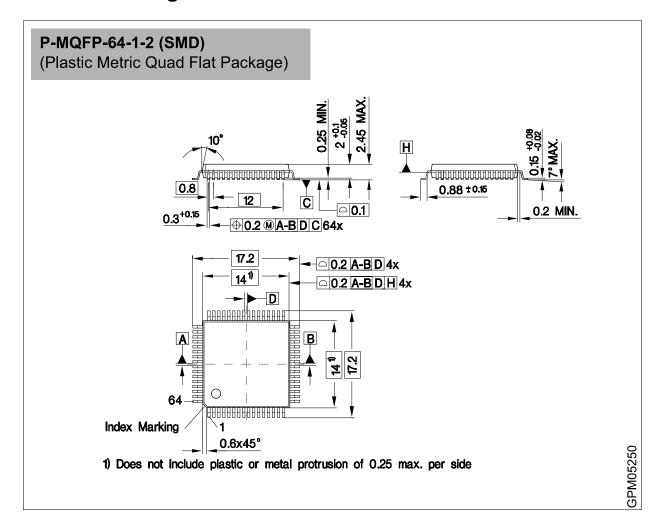

| 8               | Package Outlines                                           |

|-----------------|------------------------------------------------------------|

| 7.3             | Programming the IOM-2 SICOFI-2 Tone Generators             |

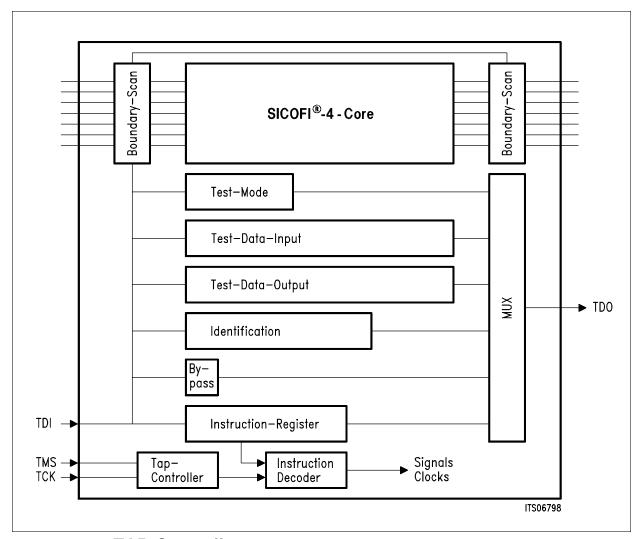

| 7.1.2<br>7.2    | The TAP-Controller                                         |

| 7.1.2           |                                                            |

| 7.1.1           | General                                                    |

| <b>7</b><br>7.1 | Test Features84Boundary Scan84                             |

| 6.3             | IOM <sup>®</sup> -2 Interface Programming Procedure        |

| 6.2.2           | Identification Command                                     |

| 6.2.1           | Address Byte 81                                            |

| 6.2             | Monitor Channel Data Structure 81                          |

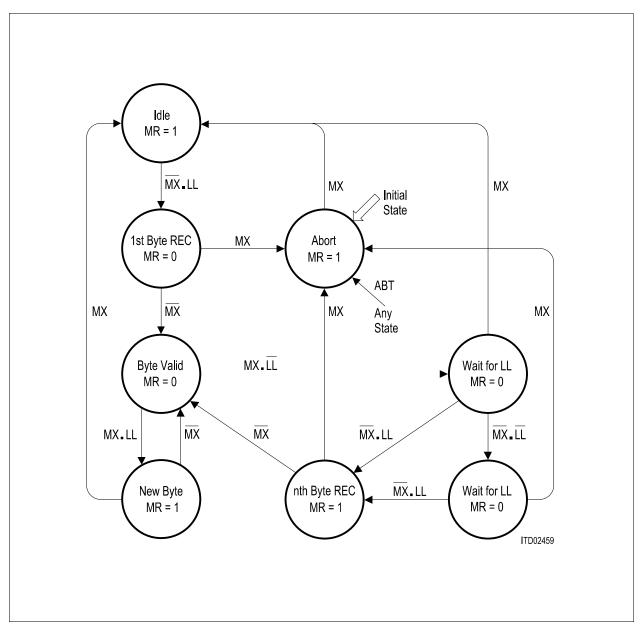

| 6.1.4           | State Diagram of the IOM-2 SICOFI-2 Monitor Receiver 80    |

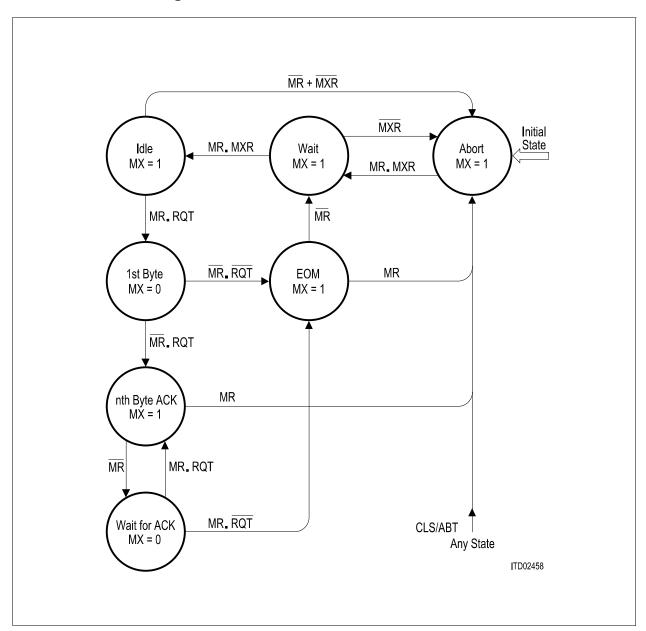

| 6.1.3           | State Diagram of the IOM-2 SICOFI-2 Monitor Transmitter 79 |

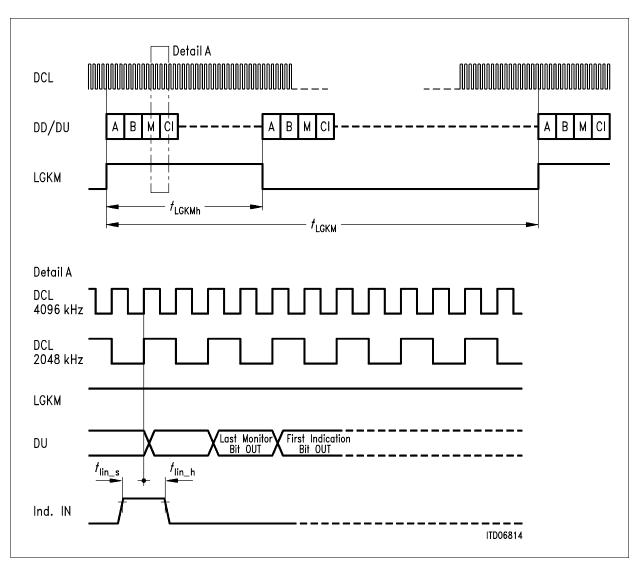

| 6.1.2           | Monitor Handshake Procedure 78                             |

| 6.1.1           | Monitor Channel Operation 77                               |

| 6.1             | IOM <sup>®</sup> -2 Interface Monitor Transfer Protocol    |

| 6               | Appendix 77                                                |

| 5.8.1           | Switching Characteristics                                  |

| 5.8             | Detector Select Timing 76                                  |

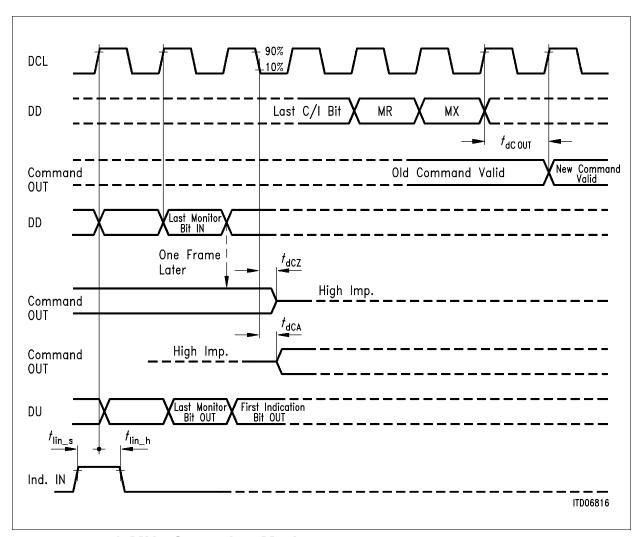

| 5.7.2           | 2-MHz Operation Mode (Mode = 0)                            |

| List of Figu | ures                                                    | Page |

|--------------|---------------------------------------------------------|------|

| Figure 1     | Pin Configuration                                       | 12   |

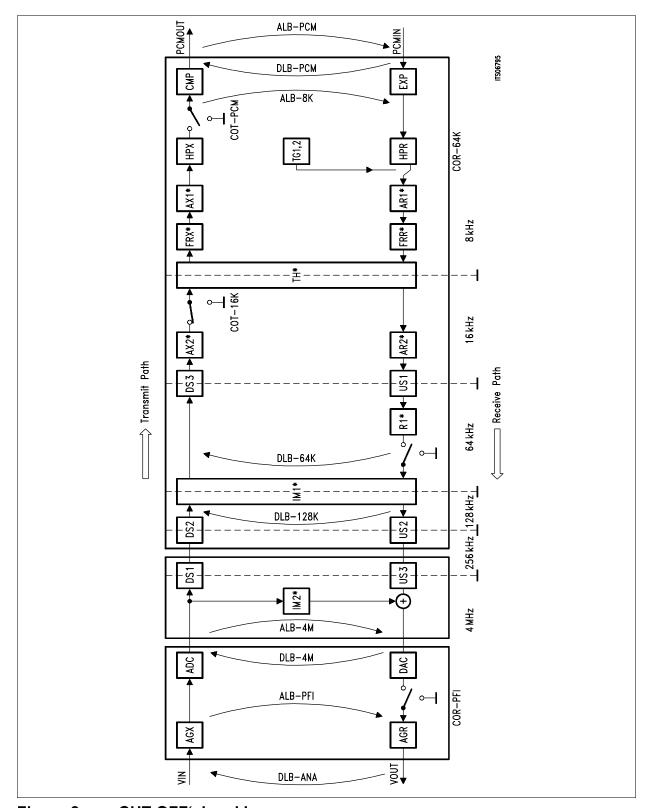

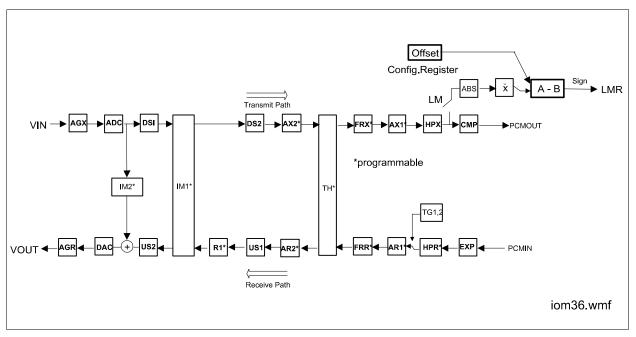

| Figure 2     | IOM-2 SICOFI-2 Signal Flow Graph                        | 17   |

| Figure 3     | IOM-2 SICOFI-2 Block Diagram                            | 19   |

| Figure 4     | IOM®-2 Interface Timing for 16 voice channels           | 20   |

| Figure 5     | IOM®-2 Interface Timing                                 | 21   |

| Figure 6     | IOM®-2 Interface Timing                                 | 22   |

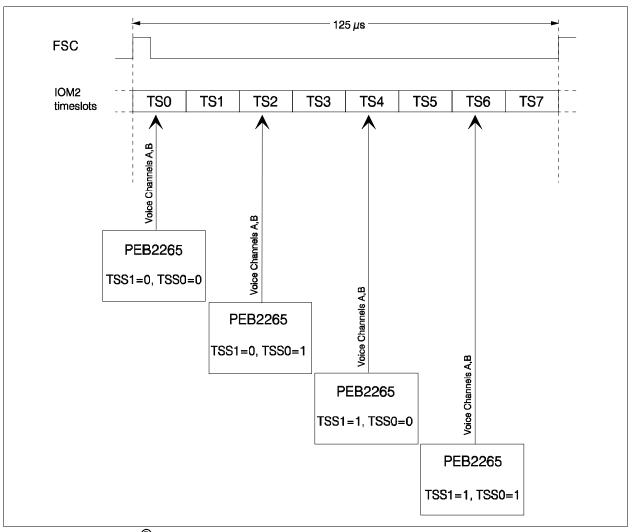

| Figure 7     | IOM®-2 Time Slot Selection                              | 24   |

| Figure 8     | CUT OFF's' and Loops                                    | 38   |

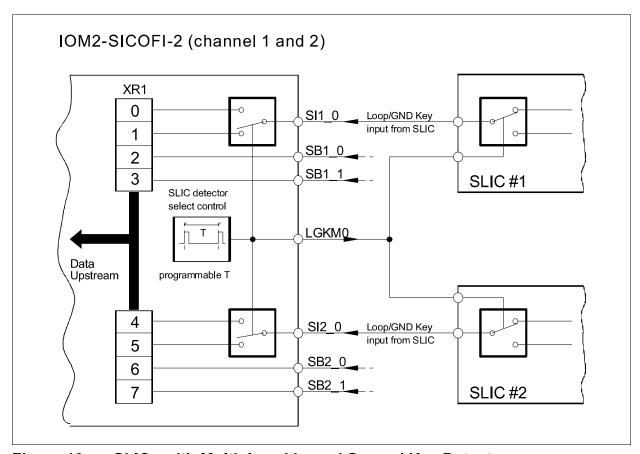

| Figure 10    | SLICs with Multiplexed Loop / Ground Key Detect         | 44   |

| Figure 11    | Data Upstream C/I Channel Byte Format                   | 47   |

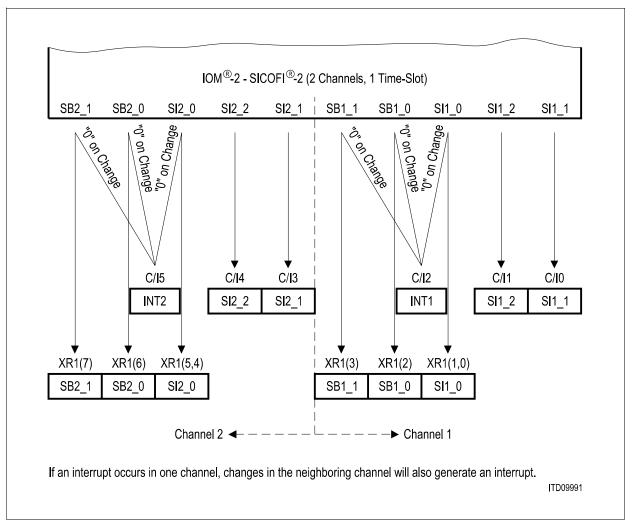

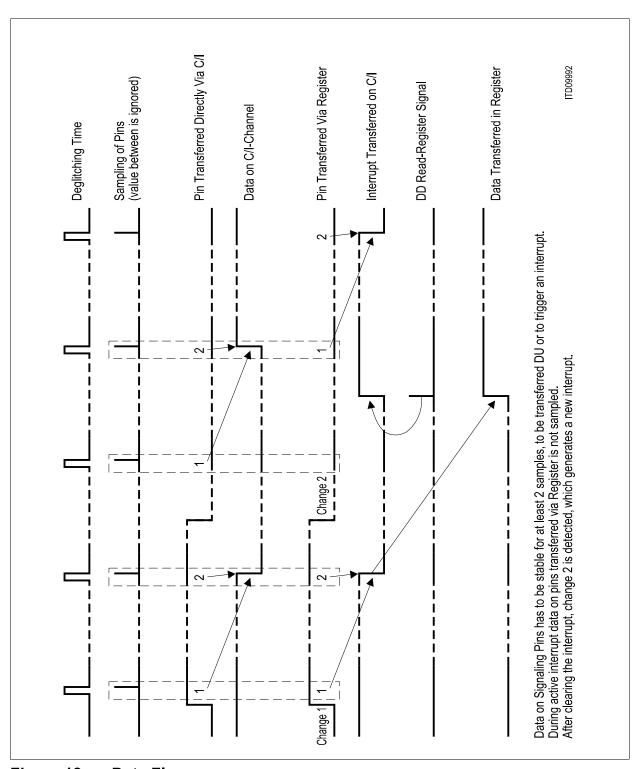

| Figure 12    | Data Flow                                               | 48   |

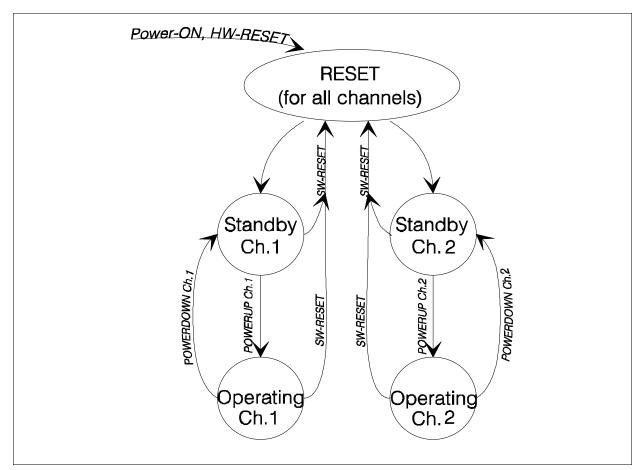

| Figure 13    | Operating Modes                                         | 49   |

| Figure 14    | QSICOS Software                                         | 53   |

| Figure 15    | Receive                                                 | 57   |

| Figure 16    | Transmit                                                | 57   |

| Figure 17    | Group Delay Distortion transmit                         | 58   |

| Figure 18    | Group Delay Distortion receive                          | 59   |

| Figure 19    | Out-of-Band Signals at Analog Input                     | 60   |

| Figure 20    | Out-of-Band Signals at Analog Output                    | 61   |

| Figure 21    | Out of Band Idle Channel Noise at Analog Output         |      |

| Figure 22    | Overload Compression                                    | 63   |

| Figure 23    | Gain Tracking                                           | 64   |

| Figure 24    | Total Distortion Measured with Sine Wave                | 65   |

| Figure 25    | Receive                                                 | 66   |

| Figure 26    | Transmit                                                | 66   |

| Figure 27    | 4-MHz Operation Mode                                    | 72   |

| Figure 28    | 2-MHz Operation Mode                                    | 73   |

| Figure 29    | 4-MHz Operation Mode                                    | 74   |

| Figure 30    | 2-MHz Operation Mode                                    | 75   |

| Figure 31    | Detector Select Timing                                  | 76   |

| Figure 32    | Monitor Channel Operation                               | 77   |

| Figure 33    | State Diagram of the IOM-2 SICOFI-2 Monitor Transmitter | 79   |

| Figure 34    | State Diagram of the IOM-2 SICOFI-2 Monitor Receiver    |      |

| Figure 35    | TAP-Controller                                          |      |

| Figure 36    | Level Metering Function                                 | 88   |

| ist of Tables |                                      | Page |  |

|---------------|--------------------------------------|------|--|

| Table 1       | Common Pins for all Channels         | 13   |  |

| Table 2       | Specific Pins for Channel 1          | 14   |  |

| Table 3       | Specific Pins for Channel 2          | 15   |  |

| Table 4       | IOM-2 Time Slots and Operating Modes | 23   |  |

| Table 5       | RESET (Basic setting mode)           | 50   |  |

| Table 6       | Standby Mode                         | 50   |  |

| Table 7       | Single Frequency Distortion          | 67   |  |

| Table 8       | Transhybrid Loss                     | 67   |  |

|               |                                      |      |  |

#### 1 Overview

The two Channel Codec Filter PEB 2265 IOM-2 – SICOFI-2 is the logic continuation of a well-established family of Siemens Codec-Filter-ICs.

The IOM-2 – SICOFI-2 is a fully integrated PCM codec and filter fabricated in low power 1  $\mu m$  CMOS technology for applications in digital communication systems. Based on an advanced digital filter concept, the PEB 2265 provides excellent transmission performance and high flexibility. The new filter concept (second generation) lends to a maximum of independence between the different filter blocks. Each filter block can be seen like an one to one representative of the corresponding network element.

Only very few external components are needed, to complete the functionality of the IOM-2 – SICOFI-2. The internal level accuracy is based on a very accurate bandgap reference. The frequency behavior is mainly determined by digital filters, which do not have any fluctuations. As a result of the new ADC and DAC concepts linearity is only limited by second order parasitic effects. Although the device works with only one single 5-V supply there is a very good dynamic range available.

# Two Channel Codec Filter with IOM-2 Interface SICOFI-2

**PEB 2265**

#### Version 1.1

#### 1.1 Features

- Single chip CODEC and FILTER to handle two CO- or PABX-channels

- Specification according to relevant CCITT, EIA and LSSGR recommendations

- · Digital signal processing technique

- Programmable interface optimized to current feed SLICs and transformer solutions

- Four pin serial IOM-2 Interface

- Single power supply 5 V

- Advanced low power 1µm analog CMOS technology

- Standard 64-pin P-MQFP-64 package

- High performance Analog to Digital Conversion

- High performance Digital to Analog Conversion

- · Programmable digital filters to adapt the transmission behavior especially for

- AC impedance matching

- transhybrid balancing

- frequency response

- gain

- Advanced test capabilities

- all digital pins can be tested within a boundary scan scheme (IEEE 1149.1)

- five digital loops

- four analog loops

- two programmable tone generators per channel

- · Comprehensive development platform available

- software for automatic filter coefficient calculation QSICOS

- Hardware development board STUT 2465

| Туре     | Package                       |

|----------|-------------------------------|

| PEB 2265 | <dev_package1></dev_package1> |

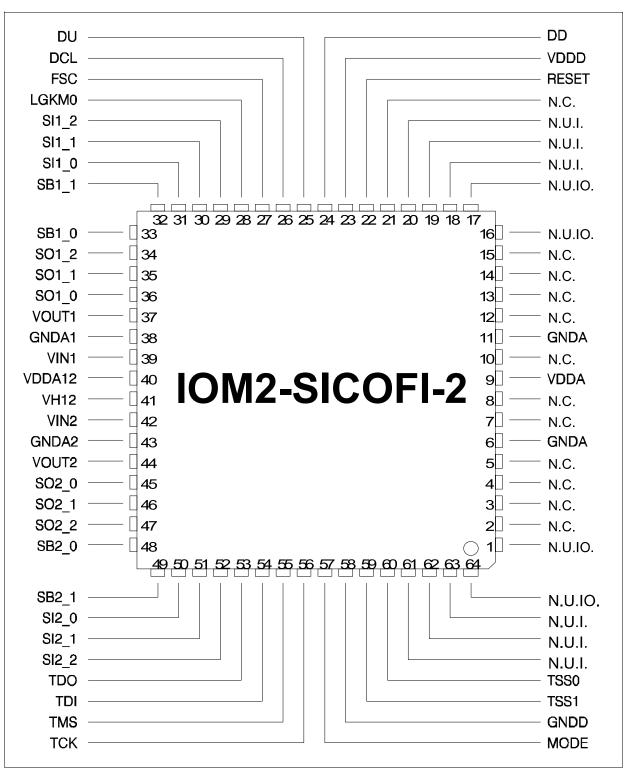

## **1.2 Pin Configuration** (top view)

Figure 1 Pin Configuration

# 1.3 Pin Definition and Functions

## 1.3.1 Common Pins for all Channels

Table 1

Common Pins for all Channels

| Pin No.              | Symbol | Input (I)<br>Output (O) | Function                                                                                                                       |

|----------------------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 23                   | VDDD   | I                       | + 5 V supply for the digital circuitry <sup>1)</sup>                                                                           |

| 58                   | GNDD   | I                       | Ground Digital, not internally connected to GNDA 1, 2 or GNDA (pin 6 and pin 11). All digital signals are referred to this pin |

| 40                   | VDDA12 | I                       | + 5 V Analog supply voltage for channel 1 and 2 <sup>1)</sup>                                                                  |

| 9                    | VDDA   | I                       | + 5 V Analog supply voltage <sup>1)</sup>                                                                                      |

| 6,11                 | GNDA   | I                       | Ground Analog, not internally connected to GNDD or GNDA1,2                                                                     |

| 27                   | FSC    | 1                       | IOM-2: Frame synchronization clock, 8 kHz                                                                                      |

| 26                   | DCL    | I                       | IOM-2: Data clock, 2048 kHz or 4096 kHz depending on MODE                                                                      |

| 25                   | DU     | 0                       | IOM-2: Data upstream, open drain output                                                                                        |

| 24                   | DD     | I                       | IOM-2: Data downstream, input                                                                                                  |

| 22                   | RESET  | I                       | Reset input - forces the device to the default mode, active high                                                               |

| 57                   | MODE   | I                       | IOM-2: Mode Selection                                                                                                          |

| 60                   | TSS0   | I                       | IOM-2: Time slot selection pin 0                                                                                               |

| 59                   | TSS1   | I                       | IOM-2: Time slot selection pin 1                                                                                               |

| 56                   | TCK    | I                       | Boundary scan: Test Clock                                                                                                      |

| 55                   | TMS    | I                       | Boundary scan: Test Mode Select                                                                                                |

| 54                   | TDI    | I                       | Boundary scan: Test Data Input                                                                                                 |

| 53                   | TDO    | 0                       | Boundary scan: Test Data Output                                                                                                |

| 28                   | LGKM0  | 0                       | Loop/Ground Key Multiplexing output 0 for channel 1, 2                                                                         |

| 41                   | VH12   | I/O                     | Reference voltage for channel 1 and 2, has to be connected via a 220 nF cap. to ground                                         |

| 18,19,20<br>61,62,63 | N.U.I. | I                       | None Usable Input, tie directly to Digital Ground                                                                              |

Table 1 Common Pins for all Channels

| Pin No.                                | Symbol  | Input (I)<br>Output (O) | Function                                                                     |

|----------------------------------------|---------|-------------------------|------------------------------------------------------------------------------|

| 1,16<br>17,64                          | N.U.IO. | I/O                     | None Usable Input/Output, tie via a Pull-Down-<br>Resistor to Digital Ground |

| 2,3,4,5,7<br>8,10,12<br>13,14,15<br>21 | N.C.    |                         | not connected                                                                |

<sup>1)</sup> A 100 nF cap. should be used for blocking these pin.

# 1.3.2 Specific Pins for Channel 1

Table 2 Specific Pins for Channel 1

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                          |

|---------|--------|-------------------------|---------------------------------------------------------------------------------------------------|

| 38      | GNDA1  | I                       | Ground Analog for channel 1, not internally connected to GNDD or GNDA2 or GNDA (pin 6 and pin 11) |

| 39      | VIN1   | I                       | Analog voice (voltage) input for channel 1                                                        |

| 37      | VOUT1  | 0                       | Analog voice (voltage) output for channel 1                                                       |

| 31      | SI1_0  | I                       | Signaling indication input pin 0 for channel 1                                                    |

| 30      | SI1_1  | I                       | Signaling indication input pin 1 for channel 1                                                    |

| 29      | SI1_2  | I                       | Signaling indication input pin 2 for channel 1                                                    |

| 36      | SO1_0  | 0                       | Signaling command output pin 0 for channel 1                                                      |

| 35      | SO1_1  | 0                       | Signaling command output pin 1 for channel 1                                                      |

| 34      | SO1_2  | 0                       | Signaling command output pin 2 for channel 1                                                      |

| 33      | SB1_0  | I/O                     | Bi-directional signal. Command indication pin 0 for channel 1                                     |

| 32      | SB1_1  | I/O                     | Bi-directional signal. Command indication pin 1 for channel 1                                     |

# 1.3.3 Specific Pins for Channel 2

Table 3 Specific Pins for Channel 2

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                          |

|---------|--------|-------------------------|---------------------------------------------------------------------------------------------------|

| 43      | GNDA2  | I                       | Ground Analog for channel 2, not internally connected to GNDD or GNDA1 or GNDA (pin 6 and pin 11) |

| 42      | VIN2   | I                       | Analog voice (voltage) input for channel 2                                                        |

| 44      | VOUT2  | 0                       | Analog voice (voltage) output for channel 2                                                       |

| 50      | SI2_0  | I                       | Signaling indication input pin 0 for channel 2                                                    |

| 51      | SI2_1  | I                       | Signaling indication input pin 1 for channel 2                                                    |

| 52      | SI2_2  | I                       | Signaling indication input pin 2 for channel 2                                                    |

| 45      | SO2_0  | 0                       | Signaling command output pin 0 for channel 2                                                      |

| 46      | SO2_1  | 0                       | Signaling command output pin 1 for channel 2                                                      |

| 47      | SO2_2  | 0                       | Signaling command output pin 2 for channel 2                                                      |

| 48      | SB2_0  | I/O                     | Bi-directional signal. command indication pin 0 for channel 2                                     |

| 49      | SB2_1  | I/O                     | Bi-directional signal. command indication pin 1 for channel 2                                     |

#### 1.4 IOM-2 SICOFI-2 Principles

The change from 2  $\mu m$  to 1  $\mu m$  CMOS process requires new concepts in the realization of the analog functions. High performance (in the terms of gain, speed, stability ...) 1  $\mu m$  CMOS devices can not withstand more than 5.5 V of supply voltage. On that account the negative supply voltage  $V_{SS}$  of the previous SICOFIs will be omitted. This is a benefit for the user but it makes a very high demand on the analog circuitry.

ADC and DAC are changed to Sigma-Delta-concepts to fulfill the stringent requirements on the dynamic parameters.

Using 1  $\mu$ m CMOS does not only lend to problems – it is the only acceptable solution in terms of area and power consumption for the integration of more then two SICOFI channels on a single chip.

It is rather pointless to implement 2 codec-filter-channels on one chip with pure analog circuitry. The use of a DSP-concept (the SICOFI and the SICOFI-2-approach) for this function seems to be a must for an adequate two channel architecture.

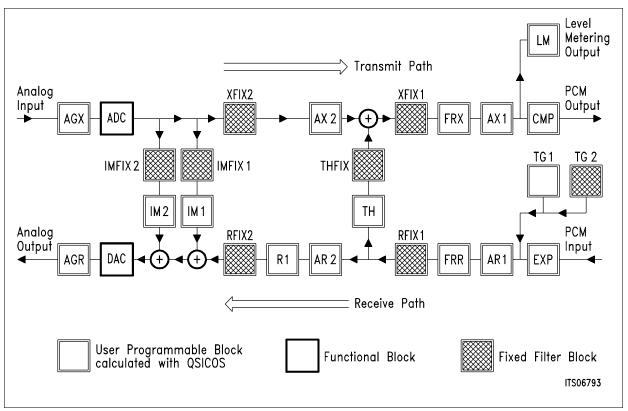

#### 1.5 IOM-2 SICOFI-2 Signal Flow Graph (for either channel)

Figure 2 IOM-2 SICOFI-2 Signal Flow Graph

#### 1.5.1 Transmit Path

The analog input signal has to be DC-free connected by an external capacitor because there is an internal virtual reference ground potential. After passing a simple antialiasing prefilter (PREFI) the voice signal is converted to a 1-bit digital data stream in the Sigma-Delta-converter. The first downsampling steps are done in fast running digital hardware filters. The following steps are implemented in the micro-code which has to be executed by the central Digital Signal Processor. This DSP-machine is able to handle the workload for all two channels. At the end the fully processed signal (flexibly programmed in many parameters) is transferred to the IOM-2 interface in a PCM-compressed signal representation.

#### 1.5.2 Receive Path

The digital input signal is received via the IOM-2 interface. Expansion, PCM-law-pass-filtering, gain correction and frequency response correction are the next steps which are done by the DSP-machine. The upsampling interpolation steps are again processed by fast hardware structures to reduce the DSP-workload. The upsampled 1-bit data stream is then converted to an analog equivalent which is smoothed by a POST-Filter (POFI). As the signal VOUT is also referenced to an internal virtual ground potential, an external capacitor is required for DC-decoupling.

## 1.5.3 Loops

There are two loops implemented. The first is to generate the AC-input impedance (IM) and the second is to perform a proper hybrid balancing (TH). A simple extra path IM2 (from the transmit to the receive path) supports the impedance matching function.

#### 1.5.4 Test Features

There are four analog and five digital test loops implemented in the IOM-2 – SICOFI-2. For special tests it is possible to "Cut Off" the receive and the transmit path at two different points.

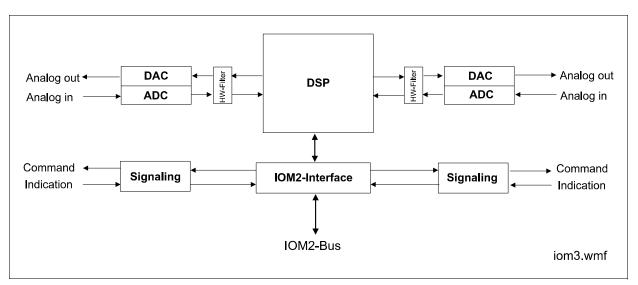

#### 1.6 IOM-2 SICOFI-2 Block Diagram

Figure 3 IOM-2 SICOFI-2 Block Diagram

The IOM-2 – SICOFI-2 bridges the gap between analog and digital voice signal transmission in modern telecommunication systems. High performance oversampling Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC) provide the required conversion accuracy. Analog antialiasing prefilters (PREFI) and smoothing postfilters (POFI) are included. The connection between the ADC and the DAC (with high sampling rate) and the DSP, is done by specific Hardware Filters, for filtering like interpolation and decimation. The dedicated Digital Signal Processor (DSP) handles all the algorithms necessary e.g. for PCM bandpass filtering, sample rate conversion and PCM companding. The IOM-2 Interface handles digital voice transmission, IOM-2 – SICOFI-2 feature control and transparent access to the IOM-2 – SICOFI-2 command and indication pins. To program the filters, precalculated sets of coefficients are downloaded from the system to the on chip coefficient ram (CRAM).

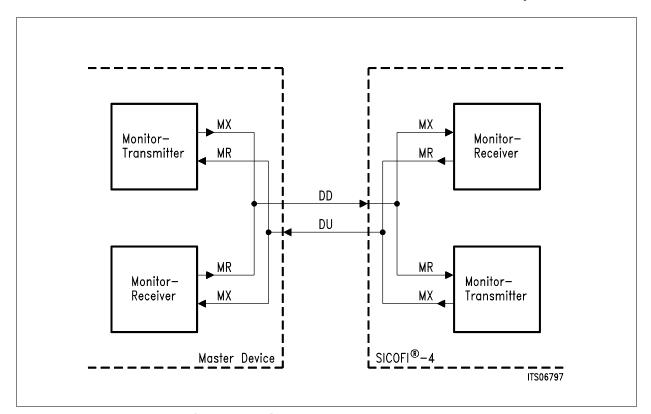

#### 1.7 IOM®-2 Interface

The IOM-2 Interface consists of two data lines and two clock lines. DU (data upstream) carries data from the IOM-2 – SICOFI-2 to a master device. This master device performs the interface between the PCM-backplane, the μController and up to 24 IOM-2 – SICOFI-2's. DD (data downstream) carries data from the master device to the IOM-2-SICOF-2. A frame synchronization clock signal (8 kHz, FSC) as well as a data clock signal (2048 kHz or 4096 kHz DCL) has to be supplied to the IOM-2 – SICOFI-2. The IOM-2 – SICOFI-2 handles data as described in the IOM-2 specification for analog devices.

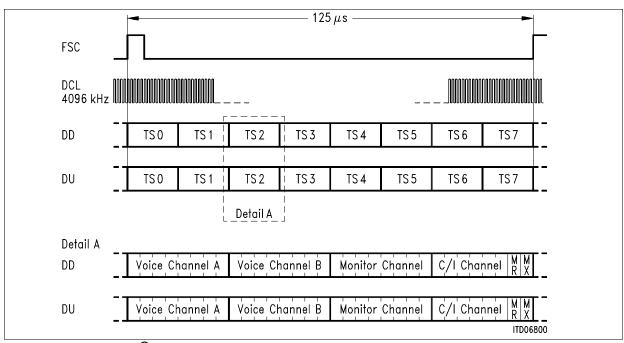

# 1.7.1 IOM®-2 Interface Timing for 16 voice channels (per 8 kHz frame)

Figure 4 IOM®-2 Interface Timing for 16 voice channels

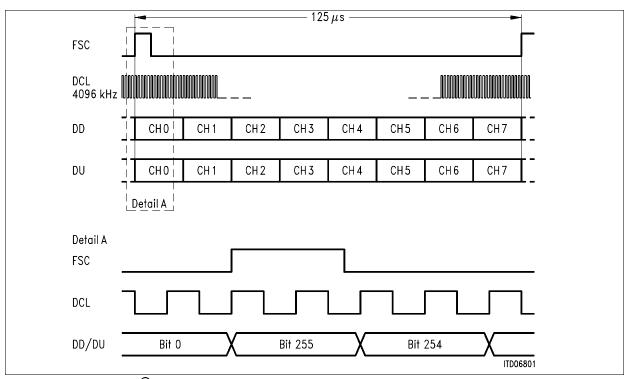

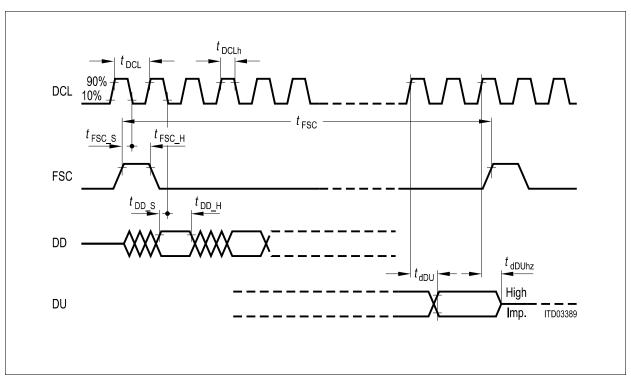

# 1.7.2 IOM®-2 Interface Timing

(DCL = 4096 kHz, MODE = 1, per 8 kHz frame)

Figure 5 IOM®-2 Interface Timing

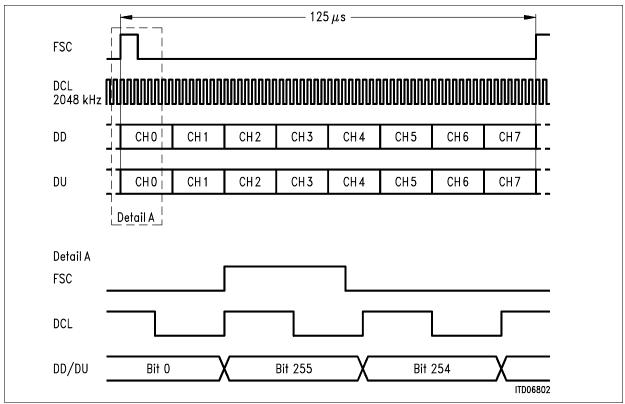

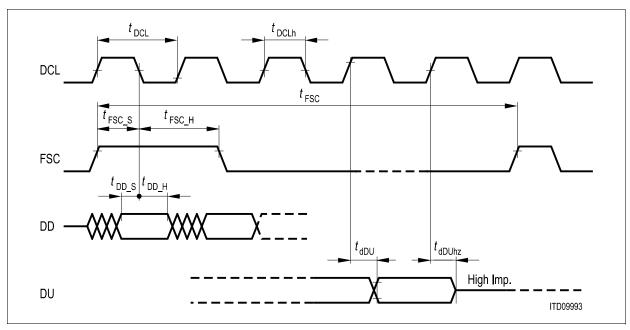

# 1.7.3 IOM®-2 Interface Timing

(DCL = 2048 kHz, MODE = 0)

Figure 6 IOM®-2 Interface Timing

## 1.7.4 IOM®-2 Time Slot Selection

The two channels (1 and 2) of the IOM-2 – SICOFI-2 can be assigned to 4 time slots by pin-strapping the pins TSS0 and TSS1 (TS0, TS2, TS4, TS6). The IOM-2 operating mode is selected by the MODE pin.

Table 4 IOM-2 Time Slots and Operating Modes

| TSS1 | TSS0 | MODE | IOM <sup>®</sup> -2 Operating Mode |

|------|------|------|------------------------------------|

| 0    | 0    | 1    | Time slot 0; DCL= 4096 kHz         |

| 0    | 1    | 1    | Time slot 2; DCL= 4096 kHz         |

| 1    | 0    | 1    | Time slot 4; DCL= 4096 kHz         |

| 1    | 1    | 1    | Time slot 6; DCL= 4096 kHz         |

| 0    | 0    | 0    | Time slot 0; DCL= 2048 kHz         |

| 0    | 1    | 0    | Time slot 2; DCL= 2048 kHz         |

| 1    | 0    | 0    | Time slot 4; DCL= 2048 kHz         |

| 1    | 1    | 0    | Time slot 6; DCL= 2048 kHz         |

Each IOM time slot contains 2 voice channels (A and B). Those two voice channels share a common IOM-Monitor-byte as well as a common C/I-byte. The AD-bit in the Monitor command defines which of the two voice channels should be affected (programmed). (For more information on IOM-2 specific Monitor Channel Data Structure see appendix, page 77).

Figure 7 IOM<sup>®</sup>-2 Time Slot Selection

|                            |     | SS1 = 0,<br>SS0 = 0 |     | S1 = 0,<br>SS0 = 1 |     | S1 = 1,<br>SS0 = 0 | TSS1 = 1,<br>TSS0 = 1 |                  |  |

|----------------------------|-----|---------------------|-----|--------------------|-----|--------------------|-----------------------|------------------|--|

| IOM-2 SICOFI-2<br>Channels | TS  | Voice<br>Channel    | TS  | Voice<br>Channel   | TS  | Voice<br>Channel   | TS                    | Voice<br>Channel |  |

| 1                          | TS0 | Α                   | TS2 | Α                  | TS4 | Α                  | TS6                   | Α                |  |

| 2                          | TS0 | В                   | TS2 | В                  | TS4 | В                  | TS6                   | В                |  |

#### **Programming the IOM-2 SICOFI-2**

## 2 Programming the IOM-2 SICOFI-2

With the appropriate commands, the IOM-2 – SICOFI-2 can be programmed and verified very flexibly via the IOM-2 Interface monitor channel.

Data transfer to the IOM-2 – SICOFI-2 starts with a SICOFI-specific address byte ( $81_H$ ). With the second byte one of 3 different types of commands (SOP, XOP and COP) is selected. Each of those can be used as a write or read command. Due to the extended IOM-2 – SICOFI-2 feature control facilities, SOP, COP and XOP commands contain additional information (e.g. number of subsequent bytes) for programming (write) and verifying (read) the IOM-2 – SICOFI-2 status.

A write command is followed by up to 8 bytes of data. The IOM-2 – SICOFI-2 responds to a read command with its IOM-2 specific address and the requested information, that is up to 8 bytes of data (see programming Procedure, page 25).

**Attention:** Each byte on the monitor channel, has to be sent twice at least, according to the IOM-2 Monitor handshake procedure (For more information on IOM-2 specific Monitor Channel Data Structure see appendix, page 77).

#### **Programming the IOM-2 SICOFI-2**

#### 2.1 Types of Monitor Bytes

The 8-bit Monitor Bytes have to be interpreted as either commands or status information stored in Configuration Registers or the Coefficient RAM. There are three different types of IOM-2 – SICOFI-2 commands which are selected by bit 3 and 4 as shown below.

**SOP STATUS OPERATION:** IOM-2 – SICOFI-2 status setting/monitoring

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

|     |   |   |   | 1 | 0 |   |   |   |

XOP EXTENDED OPERATIO:C/I channel configuration/evaluation

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

|     | Х |   |   | 1 | 1 |   |   |   |

COP COEFFICIENT OPERATION: filter coefficient setting/monitoring

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

|     |   |   |   | 0 |   |   |   |   |

## **Storage of Programming Information:**

4 configuration registers per channel: CR1, CR2, CR3, CR4 accessed by SOP

commands

4 common configuration registers: XR1, XR2, XR3 and XR4 accessed by

XOP commands (the contents are valid for two voice channels i.e. 1 IOM-2 time slot)

two voice channels i.e. i join-2 time sie

1 coefficient RAM per channel: CRAM accessed by COP commands

0

## **Preliminary**

## **Programming the IOM-2 SICOFI-2**

#### 2.2 **IOM-2 SICOFI-2 Commands**

#### 2.2.1 **SOP - Write Commands**

| DD               | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit |

|------------------|---|---|---|----|-----|---|---|---|-----|

| Address          | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |     |

| SOP-Write 1 Byte |   | 0 |   | 1  | 0   | 0 | 0 | 1 |     |

| CR1              |   |   |   | Da | ata |   |   |   |     |

| 1 | Ь | 5 | 4  | 3  | 2 | 1 | U | טט |

|---|---|---|----|----|---|---|---|----|

|   |   |   | Id | le |   |   |   |    |

|   |   |   | Id | le |   |   |   |    |

|   |   |   | ld | le |   |   |   |    |

| DD                | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit |

|-------------------|---|---|---|----|-----|---|---|---|-----|

| Address           | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |     |

| SOP-Write 2 Bytes |   | 0 |   | 1  | 0   | 0 | 1 | 0 |     |

| CR2               |   |   |   | Da | ata |   |   | • |     |

| CR1               |   |   |   | Da | ata |   |   |   |     |

| 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | DU |

|---|---|---|----|----|---|---|---|----|

|   |   |   | ld | le |   |   |   |    |

|   |   |   | ld | le |   |   |   |    |

|   |   |   | ld | le |   |   |   |    |

|   |   |   | Id | le |   |   |   |    |

| DD                | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit |

|-------------------|---|---|---|----|-----|---|---|---|-----|

| Address           | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |     |

| SOP-Write 3 Bytes |   | 0 |   | 1  | 0   | 0 | 1 | 1 |     |

| CR3               |   |   |   | Da | ata |   |   |   |     |

| CR2               |   |   |   | Da | ata |   |   |   |     |

| CR1               |   |   |   | Da | ata |   |   |   |     |

| 1 | О | Э | 4  | 3  | 2 | ı | U | ט |

|---|---|---|----|----|---|---|---|---|

|   |   |   | ld | le |   |   |   |   |

|   |   |   | ld | le |   |   |   |   |

|   |   |   | ld | le |   |   |   |   |

|   |   |   | ld | le |   |   |   |   |

|   |   |   | ld | le |   |   |   |   |

|   |   |   |    |    |   |   |   |   |

| DD                | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | DU |

|-------------------|---|---|---|----|-----|---|---|---|-----|---|---|---|----|-----|---|---|---|----|

| Address           | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |     |   |   |   | ld | lle |   |   |   |    |

| SOP-Write 4 Bytes |   | 0 |   | 1  | 0   | 1 | 0 | 0 |     |   |   |   | ld | lle |   |   |   |    |

| CR4               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | lle |   |   |   |    |

| CR3               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | lle |   |   |   |    |

| CR2               |   |   |   | Da | ata |   |   |   |     |   |   |   | Id | lle |   |   |   |    |

| CR1               |   |   |   | Da | ata |   |   |   |     |   |   |   | ld | lle |   |   |   |    |

| ' | U | J | 7  | J   | _ | U |

|---|---|---|----|-----|---|---|

|   |   |   | ld | lle |   |   |

|   |   |   | ld | lle |   |   |

|   |   |   | ld | lle |   |   |

|   |   |   | ld | lle |   |   |

|   |   |   | ld | lle |   |   |

|   |   |   | ld | lle |   |   |

## **Programming the IOM-2 SICOFI-2**

## 2.2.2 XOP - Write Commands

| DD                | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7  | 6  | 5 | 4  | 3  | 2 | 1 | 0 | DU |

|-------------------|---|---|---|----|-----|---|---|---|-----|----|----|---|----|----|---|---|---|----|

| Address           | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |     | ld | le |   |    |    |   |   |   |    |

| XOP-Write 2 Bytes |   | 0 |   | 1  | 1   | 0 | 1 | 0 |     |    |    |   | ld | le |   |   |   |    |

| XR2               |   |   |   | Da | ata |   |   |   |     |    |    |   | Id | le |   |   |   |    |

| XR1               |   |   |   | Da | ata |   |   |   |     |    |    |   | Id | le |   |   |   |    |

| , 0  | U | •  | •  | _ | • | • |

|------|---|----|----|---|---|---|

| Idle |   |    |    |   |   |   |

|      |   | ld | le |   |   |   |

|      |   | ld | le |   |   |   |

|      |   | Id | le |   |   |   |

| DD                | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Bit | 7 6 5 4 3 2 1 0 | DU |

|-------------------|---|---|---|----|-----|---|---|---|-----|-----------------|----|

| Address           | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |     | Idle            |    |

| XOP-Write 3 Bytes |   | 0 |   | 1  | 1   | 0 | 1 | 0 |     | Idle            |    |

| XR3               |   |   | • | Da | ata |   | • | • |     | Idle            |    |

| XR2               |   |   |   | Da | ata |   |   |   |     | Idle            |    |

| XR1               |   |   |   | Da | ata |   |   |   |     | Idle            |    |

| Idle |

|------|

| Idle |

| Idle |

| Idle |

| Idle |

## **Programming the IOM-2 SICOFI-2**

#### **COP - Write Commands** 2.2.3

| DD | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Bit |

|----|---|---|---|---|---|---|---|---|-----|

|    |   |   |   |   |   |   |   |   |     |

| Address           | 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 |

|-------------------|---|---|---|----|-----|---|---|---|

| COP-Write 4 Bytes |   | 0 |   | 0  | 1   |   |   |   |

| Coeff. 4          |   |   |   | Da | ata |   |   |   |

| Coeff. 3          |   |   |   | Da | ata |   |   |   |

| Coeff. 2          |   |   |   | Da | ata |   |   |   |

| Coeff. 1          |   |   |   | Da | ata |   |   |   |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | DU |

|---|---|---|---|---|---|---|---|----|

|   | _ | _ |   | _ | _ |   | _ |    |

| ldle |  |

|------|--|

| Idle |  |

| Idle |  |

| Idle |  |

| Idle |  |

| ldle |  |

DD

|                   | •    | • | • | •  | •   | _ | • | • |

|-------------------|------|---|---|----|-----|---|---|---|

| Address           | 1    | 0 | 0 | 0  | 0   | 0 | 0 | 1 |

| COP-Write 8 Bytes |      | 0 |   | 0  | 0   |   |   |   |

| Coeff. 8          |      |   |   | Da | ata |   |   |   |

| Coeff. 7          |      |   |   | Da | ata |   |   |   |

| Coeff. 6          | Data |   |   |    |     |   |   |   |

| Coeff. 5          |      |   |   | Da | ata |   |   |   |

| Coeff. 4          |      |   |   | Da | ata |   |   |   |

| Coeff. 3          |      |   |   | Da | ata |   |   |   |

| Coeff. 2          |      |   |   | Da | ata |   |   |   |

| Coeff. 1          |      |   |   | Da | ata |   |   |   |

|                   |      |   |   |    |     |   |   |   |

| Idle |

|------|

| ldle |

| ldle |

| ldle |

| ldle |

| Idle |

| Idle |

| Idle |

| ldle |

| ldle |

|      |

## **Programming the IOM-2 SICOFI-2**

# 2.2.4 SOP - Read Commands

| DD              | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|-----------------|---|---|---|----|----|---|---|---|-----|

| Address         | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| SOP-Read 1 Byte |   | 1 |   | 1  | 0  | 0 | 0 | 1 |     |

|                 |   |   |   | Id | le |   | • | • |     |

|                 |   |   |   | ld | le |   |   |   |     |

| 1 | О | 5 | 4   | 3       | 2 | 1 | U | טט |

|---|---|---|-----|---------|---|---|---|----|

|   |   |   |     |         |   |   |   |    |

|   |   |   |     |         |   |   |   |    |

| 1 | 0 | 0 | 0   | Address |   |   |   |    |

|   |   |   | CR1 |         |   |   |   |    |

| DD               | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|------------------|---|---|---|----|----|---|---|---|-----|

| Address          | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| SOP-Read 2 Bytes |   | 1 |   | 1  | 0  | 0 | 1 | 0 |     |

|                  |   |   |   | Id | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

| 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | DU      |

|---|---|---|----|-----|---|---|---|---------|

|   |   |   | ld | le  |   |   |   |         |

|   |   |   | ld | le  |   |   |   |         |

| 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 | Address |

|   |   |   | Da | ata |   |   |   | CR2     |

|   |   |   | Da | ata |   |   |   | CR1     |

| DD               | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|------------------|---|---|---|----|----|---|---|---|-----|

| Address          | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| SOP-Read 3 Bytes |   | 1 |   | 1  | 0  | 0 | 1 | 1 |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   |    |    |   |   |   | 4   |

| ss |

|----|

|    |

|    |

|    |

|    |

| DD               | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|------------------|---|---|---|----|----|---|---|---|-----|

| Address          | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| SOP-Read 4 Bytes |   | 1 |   | 1  | 0  | 1 | 0 | 0 |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   |    |    |   |   |   |     |

| 7 | 6    | 5 | 4  | 3   | 2   | 1 | 0 | DU      |

|---|------|---|----|-----|-----|---|---|---------|

|   |      |   | ld | le  |     |   |   |         |

|   |      |   | ld | le  |     |   |   |         |

| 1 | 0    | 0 | 0  | 0   | 0   | 0 | 1 | Address |

|   |      |   | Da | ata |     |   |   | CR4     |

|   |      |   | Da | ata |     |   |   | CR3     |

|   | Data |   |    |     |     |   |   | CR2     |

|   |      |   | Da |     | CR1 |   |   |         |

|   |      |   |    |     |     |   |   |         |

## **Programming the IOM-2 SICOFI-2**

# 2.2.5 XOP - Read Commands

| DD              | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|-----------------|---|---|---|----|----|---|---|---|-----|

| Address         | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| XOP-Read 1 Byte |   | 1 |   | 1  | 1  | 0 | 0 | 1 |     |

|                 |   |   |   | ld | le |   |   |   |     |

|                 |   |   |   | ld | le |   |   |   |     |

| 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | DU      |

|---|---|---|----|-----|---|---|---|---------|

|   |   |   | ld | le  |   |   |   |         |

|   |   |   | ld | le  |   |   |   |         |

| 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 | Address |

|   |   |   | Da | ata |   |   |   | XR1     |

| DD               | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|------------------|---|---|---|----|----|---|---|---|-----|

| Address          | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| XOP-Read 2 Bytes |   | 1 |   | 1  | 1  | 0 | 1 | 0 |     |

|                  |   |   |   | Id | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

| 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | DU      |

|---|---|---|----|-----|---|---|---|---------|

|   |   |   | Id | le  |   |   |   |         |

|   |   |   |    |     |   |   |   |         |

| 1 | 0 | 0 | 0  | 0   | 0 | 0 | 1 | Address |

|   |   |   | Da | ata |   |   |   | XR2     |

|   |   |   | Da | ata |   |   |   | XR1     |

| DD               | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | Bit |

|------------------|---|---|---|----|----|---|---|---|-----|

| Address          | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |     |

| XOP-Read 3 Bytes |   | 1 |   | 1  | 1  | 0 | 1 | 1 |     |

|                  |   | • |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   | ld | le |   |   |   |     |

|                  |   |   |   |    |    |   |   |   |     |

| DU      | 0 | 1 | 2 | 3          | 4        | 5 | 6 | 7 |  |

|---------|---|---|---|------------|----------|---|---|---|--|

|         |   |   |   | lle        | lo       |   |   |   |  |

| Idle    |   |   |   |            |          |   |   |   |  |

| Address | 1 | 0 | 0 | 0          | 0        | 0 | 0 | 1 |  |

| XR3     |   |   |   | ata        | Da       |   |   |   |  |

| XR2     |   |   |   | ata        | Da       |   |   |   |  |

| XR1     |   |   |   | ata        | Da       |   |   |   |  |

| XR2     |   |   |   | ata<br>ata | Da<br>Da |   |   |   |  |

## **Programming the IOM-2 SICOFI-2**

## 2.2.6 COP - Read Commands

| DD | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | DU |

|----|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|----|

|    |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |

|                  | - | - | - | -  | _  |   | - | _ |

|------------------|---|---|---|----|----|---|---|---|

| Address          | 1 | 0 | 0 | 0  | 0  | 0 | 0 | 1 |

| COP-Read 4 bytes |   | 1 |   | 0  | 1  |   |   |   |

|                  |   |   |   | ld | le |   |   |   |

|                  |   |   |   | Id | le |   |   |   |

|                  |   |   |   | ld | le |   |   |   |

|                  |   |   |   | ld | le |   |   |   |

|                  |   |   |   | ld | le |   |   |   |

|                  |   |   |   |    |    |   |   |   |

|   |   |   | ld | le      |  |  |         |

|---|---|---|----|---------|--|--|---------|

|   |   |   | ld |         |  |  |         |

| 1 | 0 | 0 | 0  | Address |  |  |         |

|   |   |   | Da | Coeff.4 |  |  |         |

|   |   |   | Da | ıta     |  |  | Coeff.3 |

|   |   |   | Da | Coeff.2 |  |  |         |

|   |   |   | Da | ıta     |  |  | Coeff.1 |

DD 7 6 5 4 3 2 1 0 Bit 7 6 5 4 3 2 1 0 DU

| טט               | 1    | О | 5 | 4  | 3  | 2 | Т | U |

|------------------|------|---|---|----|----|---|---|---|

| Address          | 1    | 0 | 0 | 0  | 0  | 0 | 0 | 1 |

| COP-Read 8 Bytes |      | 1 |   | 0  | 0  |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  | Idle |   |   |    |    |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

|                  |      |   |   | ld | le |   |   |   |

| Idle            |         |

|-----------------|---------|

| Idle            |         |

| 1 0 0 0 0 0 0 1 | Address |

| Data            | Coeff.8 |

| Data            | Coeff.7 |

| Data            | Coeff.6 |

| Data            | Coeff.5 |

| Data            | Coeff.4 |

| Data            | Coeff.3 |

| Data            | Coeff.2 |

| Data            | Coeff.1 |

# 2.2.7 Example for a Mixed Command

DD 7 6 5 4 3 2 1 0 Bit 7 6 5 4 3 2 1 0 DU

| Address           | 1           | 0 | 0 | 0  | 0   | 0 | 0 | 1 |  |  |

|-------------------|-------------|---|---|----|-----|---|---|---|--|--|

| SOP-Write 4 Bytes | 0 1 0 1 0 0 |   |   |    |     |   |   |   |  |  |

| CR4               | Data        |   |   |    |     |   |   |   |  |  |

| CR3               | Data        |   |   |    |     |   |   |   |  |  |

| CR2               |             |   |   | Da | ata |   |   |   |  |  |

| Idle |

|------|

| Idle |

| Idle |

| Idle |

| Idle |

# Programming the IOM-2 SICOFI-2

| XOP-Write 2 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |               |   |   |    |     |   |   |   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|---|---|----|-----|---|---|---|--|

| XR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CR1               |               |   |   | Da | ata |   |   |   |  |

| XR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XOP-Write 2 Bytes |               | 0 |   | 1  | 1   | 0 | 1 | 0 |  |

| COP-Write 4 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XR2               | Data          |   |   |    |     |   |   |   |  |

| Coeff. 4  Coeff. 3  Coeff. 2  Data  Coeff. 1  Idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XR1               | Data          |   |   |    |     |   |   |   |  |

| Coeff. 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | COP-Write 4 Bytes |               | 0 |   | 0  | 1   |   |   |   |  |

| Coeff. 1  SOP-Read 3 Bytes  Idle Idle Idle Idle Idle Idle Idle Idl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Coeff. 4          |               |   |   | Da | ata |   |   |   |  |

| Coeff. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Coeff. 3          |               |   |   | Da | ata |   |   |   |  |

| SOP-Read 3 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Coeff. 2          |               |   |   | Da | ata |   |   |   |  |

| Idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Coeff. 1          |               |   |   | Da | ata |   |   |   |  |

| Idle   Idle | SOP-Read 3 Bytes  |               | 1 |   | 1  | 0   | 0 | 1 | 1 |  |

| Idle   Idle |                   | Idle          |   |   |    |     |   |   |   |  |