## CoreQSGMII v2.2 User Guide

### Introduction

The CoreQSGMII provides a solution to combine four Serial Gigabit Media-Independent Interface (SGMII) lines into a single 5.0 Gbps link. The CoreQSGMII module takes each of the four Gigabit Media-Independent Interface (GMII) data stream and encodes it into 10-bit symbols per port to form a 40-bit interface to the transceiver. In the receive direction, the 40-bit symbols are decoded and converted into the receive G/MII signal set. The CoreQSGMII module is managed and monitored through the Management Data Input/Output (MDIO) interface.

The CoreQSGMII supports auto-negotiation for each of the four ports, which allows two link partners to exchange details of capabilities and hence determine the appropriate link operation characteristics, including the duplex mode and flow control direction.

### **Features**

CoreQSGMII has the Following Key Features:

- Compliant with Cisco® Systems' Proprietary QSGMII Specification, Revision 1.2

- Four Independent 10/100/1000 Mbps Ports

- Implement SGMII Adaptation for 10/100/1000 Operation of Each Port

- Implements 8b/10b Encoder/Decoder and Physical Coding Sublayer (PCS) Transmit Function for Each Port in Accordance with IEEE® Standard 802.3 Clause 36, Modified to Support QSGMII

- K28.5 Swapper on Port 0 in the Transmit Path as per the QSGMII Specification

- Comma Alignment and K28.1 Swapper on Port 0 in the Receive Path as per the QSGMII Specification

- Supports Auto-Negotiation Functionality per Port

- Supports Management Interface for Register Configuration Through MDIO Interface

- The SerDes Interface on the QSGMII IP is Configured for 40-bit, Single Lane Operating at 5.0 Gbps Speed with Fabric Interface Running at 125 MHz

# **Supported Families**

This version of CoreQSGMII supports the following families:

- PolarFire® SoC

- PolarFire

- RT PolarFire

### **Device Utilization and Performance**

CoreQSGMII has been implemented in the PolarFire device using speed grade-1. The following table lists the device utilization and performance data. The data listed in this table is indicative only. The overall device utilization and performance of the core is system dependent.

**Table 1. Device Utilization and Performance**

| Device Details | Resources |      |      | Performance<br>(MHz) |                                                                                               |

|----------------|-----------|------|------|----------------------|-----------------------------------------------------------------------------------------------|

| Family         | Device    | LUTs | DFF  | Logic Elements       |                                                                                               |

| PolarFire® SoC | MPFS250T  | 9934 | 4498 | 11168                | MDC – 100 MHz TBI_TX_CLK – 150 MHz TXCLK_Px – 150 MHz TBI_RX_CLK – 150 MHz RXCLK_Px – 150 MHz |

| PolarFire      | MPF300T   | 9939 | 4498 | 11351                | MDC – 100 MHz TBI_TX_CLK – 150 MHz TXCLK_Px – 150 MHz TBI_RX_CLK – 150 MHz RXCLK_Px – 150 MHz |

| RT PolarFire   | RTPF500T  | 9753 | 4498 | 10921                | MDC – 90 MHz TBI_TX_CLK – 150 MHz TXCLK_Px – 150 MHz TBI_RX_CLK – 150 MHz RXCLK_Px – 150 MHz  |

**Important:** The data in this table is achieved using typical synthesis and layout settings. Frequency is set to 2.5 MHz for MDC clock and 125 MHz for other clocks and speed grade is -1.

# **Table of Contents**

| Intr  | oductio | on                                    | 1  |

|-------|---------|---------------------------------------|----|

|       | Featu   | ıres                                  | 1  |

|       | Supp    | orted Families                        | 1  |

|       | Devic   | e Utilization and Performance         | 1  |

| 1.    | Funct   | tional Description                    | 4  |

|       | 1.1.    | CoreQSGMII Interfaces                 | 4  |

|       | 1.2.    | Functional Blocks                     | 5  |

| 2.    | Interfa | ace                                   | 8  |

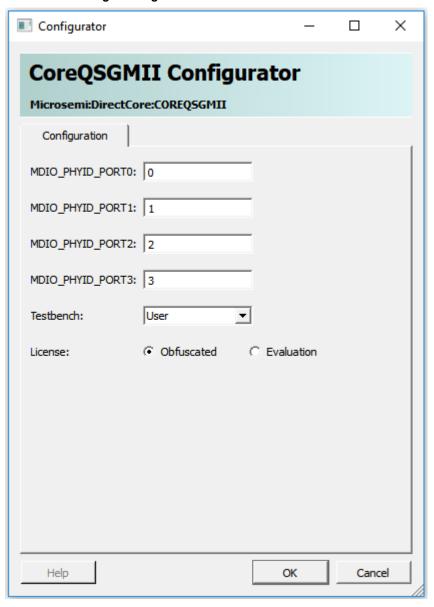

|       | 2.1.    | Configuration Parameters              | 8  |

|       | 2.2.    | I/O Signals                           | 8  |

| 3.    | Regis   | ster Map and Descriptions             | 10 |

|       | 3.1.    | Register Summary                      | 11 |

|       | 3.2.    | CoreQSGMII Register Descriptions      | 11 |

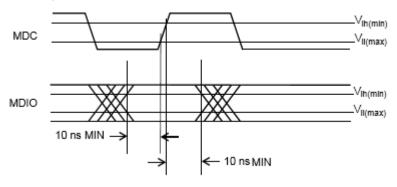

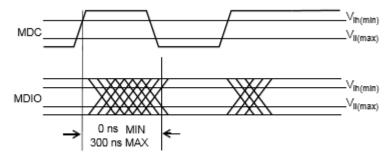

| 4.    | Timin   | g Diagrams                            | 22 |

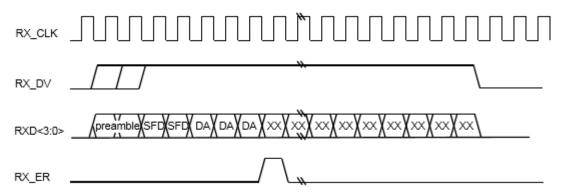

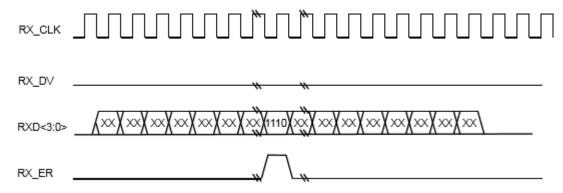

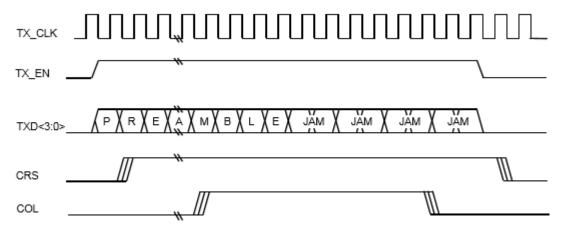

|       | 4.1.    | G/MII Timing Diagrams                 | 22 |

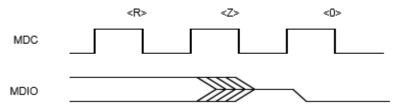

|       | 4.2.    | MDIO Timing Diagrams                  | 24 |

| 5.    | Desig   | n Constraints                         | 26 |

|       | 5.1.    | Timing Constraints                    | 26 |

| 6.    | Tool F  | Flow                                  | 27 |

|       | 6.1.    | License                               | 27 |

|       | 6.2.    | SmartDesign                           | 27 |

|       | 6.3.    | Configuring CoreQSGMII in SmartDesign | 28 |

|       | 6.4.    | Simulation Flows.                     | 28 |

|       | 6.5.    | Synthesis in Libero                   | 29 |

|       | 6.6.    | Place-and-Route in Libero             | 29 |

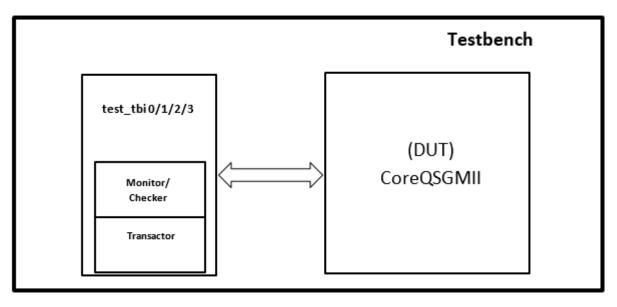

| 7.    | User    | Testbench                             | 30 |

| 8.    | Syste   | m Integration                         | 31 |

| 9.    | Revis   | ion History                           | 33 |

|       |         | FPGA Support                          |    |

|       | •       | Information                           |    |

| IVIIC |         | /icrochip Website                     |    |

|       |         | uct Change Notification Service       |    |

|       |         | omer Support                          |    |

|       |         | chip Devices Code Protection Feature  |    |

|       |         | Notice                                |    |

|       | •       | emarks                                |    |

|       |         | ty Management System                  |    |

|       | World   | lwide Sales and Service               | 37 |

## 1. Functional Description

This section describes the functional description of the CoreQSGMII.

### 1.1 CoreQSGMII Interfaces

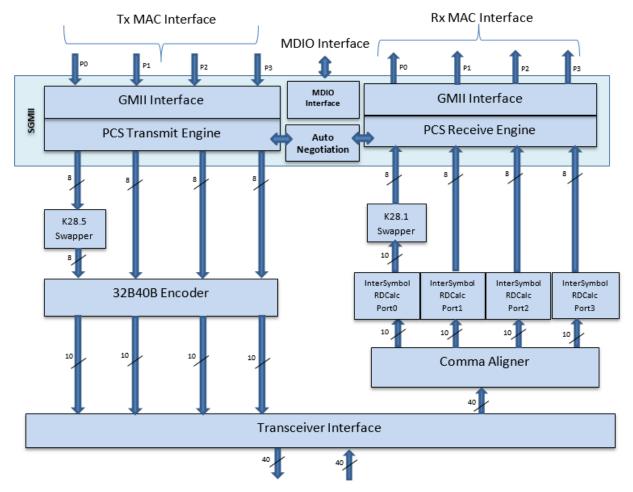

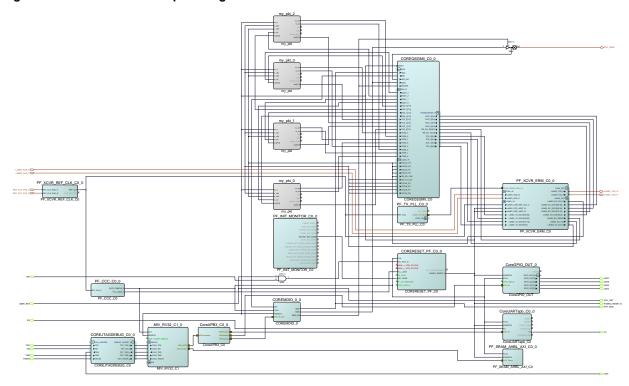

This section describes the various interfaces connected with CoreQSGMII IP core. The following figure shows the CoreQSGMII block diagram.

Figure 1-1. CoreQSGMII Block Diagram

The IP provides four independent ports of 1000/100/10 Mbps for the ethernet communication between the Physical Layer (PHY) and the Media Access Control (MAC) over a single link of 5.0 Gbps using the transceiver configured in 40-bit mode.

$\label{thm:logic_modified} The \ IP\ contains\ PCS\ functionality\ logic\ modified\ in\ compliance\ with\ Cisco's\ QSGMII\ Specification,\ Revision\ 1.2.$

CoreQSGMII consists of the following interfaces:

- · MAC-side (G/MII) interface

- Management interface

- · Transceiver interface

### 1.1.1 MAC-Side (G/MII) Interface

The IP connects to four MACs through four independent IEEE 802.3 G/MII interface.

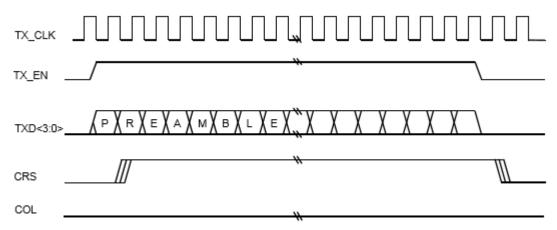

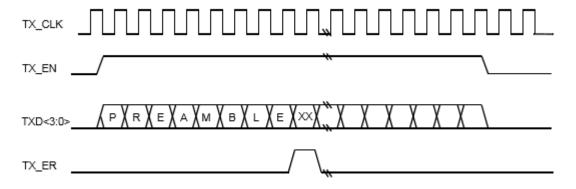

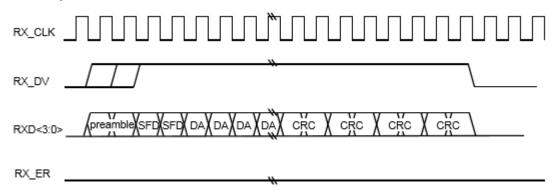

G/MII is an interface between the MAC device and the PHY. It defines speeds up to 1000 Mbps, implemented using an 8-bit data interface clocked at 125 MHz, and is backwards compatible with the Media-Independent Interface (MII) specification. It can also operates at speed of 10 or 100 Mbps as per the MII specification.

Data on the interface is framed using the IEEE Ethernet standard. It consists of the following:

- Preamble

- Start frame delimiter

- Ethernet headers

- Protocol specific data

- Cyclic Redundancy Check (CRC)

In case of G/MII transmission, there are two clocks, depending on whether the PHY is operating at 1000 Mbps or 10/100 Mbps speeds. TBI TX CLK signal is supplied to the PHY for 1000 Mbps speed, and the transmit data and the control signals are synchronized to this. Otherwise, for 10/100 Mbps, the TXCLK Px (where x represent the range of 0 to 3) signal, supplied by the PHY, is used for synchronizing those signals. This operates at either 25 MHz for 100 Mbps or 2.5 MHz for 10 Mbps connections. The RXCLK Px (where x represent the range of 0 to 3) is 2.5/25/125 MHz for 10/100/1000 respectively, is supplied from PHY/Transceiver.

It contains the logic for the PCS transmit path data conversion (repeating each data byte 10/100 times for 10/100 Mbps IEEE 802.3 G/MII and synchronization with the TBI TX CLK signal. For all the ports, the PCS transmit logic transmits only /11/ ordered sets instead of /12/ as per the QSGMII specification.

It also performs the receive path data conversion from the ten-bit interface to the G/MII data on the RXCLK Px (where x represent the range of 0 to 3) domain. It stores the data every 10/100 clocks for 10/100 Mbps respectively.

#### 1.1.2 **Management Interface**

The CoreQSGMII registers are accessed through the MDIO interface. A single MDIO interface is provided for the four independent ports. The MDIO controller in the MAC reads and writes the control and status registers of the CoreQSGMII. The MDIO interface is compliant with the IEEE 802.3z, Clause 45.

#### 1.1.3 **Transceiver Interface**

The 10-bit data from each of the SGMII instances is transferred to the transceiver interface forming 40-bit data. In the receive path, the 40-bit data from the transceiver interface is transferred to comma alignment and K28.1 detection

The transceiver is configured to operate on single lane, 40-bit mode with 125 MHz speed, at the fabric interface to give 5.0 Gbps link rate.

#### 1.2 **Functional Blocks**

CoreQSGMII contains the following blocks:

- Four SGMII blocks

- Tx/Rx swapper

- 32B40B encoder

- Comma aligner

- Receive intersymbol Running Disparity (RD) swapper

#### 1.2.1 **SGMII Block**

Each SGMII block has the G/MII interface to connect the MAC with the PHY. It performs the transmit exchange functionality, the receive exchange functionality, the auto-negotiation functionality, and the management functionality using the MDIO interface.

#### 1.2.1.1 **TEX (Transmit Exchange functionality)**

This module performs clause 36 transmit related functionality of 802.3z.

The PCS transmit functionality is modified as per QSGMII specification Revision 1.2 (Figure 1-1) on port 0 by detaching the PCS transmit functionality from the 8b/10b encoder. This is done by incorporating a "K28.5" swapper function that modifies the IDLE/I/ and Configures /C/ ordered sets by replacing every occurrence of /K28.5/ with /

DS50003421A-page 5 **User Guide** © 2022 Microchip Technology Inc.

K28.1/. The swapper function operates on the GMII octets before the 8b/10b encoding. It is important to note that the transmitter generates only /I1/ ordered set as per the QSGMII specification.

TEX operation is governed by Auto-Negotiation, which provides CFG/IDL/DAT information:

- In Configuration (CFG) mode, TEX sends /C/ ordered sets with data from Auto-Negotiation (ANX).

- In Idle (IDL) mode, TEX sends /I/ order sets.

- In Data (DAT) mode, TEX send 8b/10b encoded packets.

#### 1.2.1.2 REX (Receive Exchange functionality)

Performs clause 36, receive related functionality of 802.3z.

Performs comma alignment and passes aligned two-code-group. It determines the alignment by searching for the comma character K28.1 on the received 40-bit data, as the port 0 data can be on any of the four 10-bit lanes. After a match is found, the K28.1 swapper logic swaps the K28.1 code-group received on the port 0 with K28.5 code-group as per the QSGMII specification.

The code-groups from the PCS are decoded for 10b/8b and inspected by the receive logic.

The received 10-bit code-groups from the Ten-Bit interface performs the exact reverse procedure as that of the transmit function by undoing the swapping function introduced in the transmit path. That is, a "K28.1" swapper function replaces the received /K28.1/ with /K28.5/ for every occurrence on the port 0. The swapper logic works post the 10b/8b decoding on the 8-bit GMII octets. However, the carrier detect function operates on the 10B code-group to detect /K28.1/ for port 0.

In Auto-Negotiation mode as indicated by the transmit variable, the PCS module looks for configuration ordered sets and passes the receive configuration register contents to the ANX module.

After Auto-Negotiation completes, removes the encapsulation codes and passes the received packet.

#### 1.2.2 K28.5 Swapper

The port 0 transmit side incorporates a K28.5 swapper logic, which modifies each occurrence of K28.5 with K28.1. This is done in order to determine the port number based data alignment. The transmit data appears on the QSGMII link in the order of port 0 first, then port 1, then port 2 and, then port 3. This is repeated with the port 0 data again on the link and so on.

**Important:** The ports other than port 0 does not perform K28.5 swapping.

The following table lists the K28.5 Swapper definition for port 0.

Table 1-1. Port 0 K28.5 Swapper Definition

| Code | Ordered_Set     | Number of Code<br>Groups | Port 0 Pre-Swapper Encoding | Port 0 Post-Swapper Encoding |

|------|-----------------|--------------------------|-----------------------------|------------------------------|

| /C/  | Configuration   | _                        | Alternating /C1/ and /C2/   | Alternating /C1/ and /C2/    |

| /C1/ | Configuration 1 | 4                        | /K28.5/D21.5/Config_Reg     | /K28.1/D21.5/Config_Reg      |

| /C2/ | Configuration 2 | 4                        | /K28.5/D2.2/Config_Reg      | /K28.1/D2.2/Config_Reg       |

| /I/  | IDLE            | _                        | Correcting /I1/             | Correcting /I1/              |

| /11/ | IDLE 1          | 2                        | /K28.5/D5.6/                | /K28.1/D5.6/                 |

#### 1.2.3 32B40B Encoder

The 8-bit data from each of the SGMII blocks is formed into a 32-bit data. This module performs the 32B40B PCS encoding. The running disparity between the transmitted 10-bit symbols from each SGMII block is handled in this block.

**User Guide** DS50003421A-page 6 © 2022 Microchip Technology Inc.

#### 1.2.4 **Comma Aligner Block**

The Comma Aligner block performs alignment on two consecutive 40-bit data received from the transceiver interface. It also performs barrel shifting on the incoming data and searches for the K28.1 comma code. The detection of comma code determines the 10-bit symbol alignment with respect to port 0 data.

It provides the 40-bit aligned data with each 10-bit data going to each of the four InterSymbol RD swapper modules.

#### 1.2.5 InterSymbol RD Swapper

This block calculates the running disparity between the successive 10-bit aligned data in the receive path. The output is 10-bit data with the running disparity maintained between successive 10-bit symbols.

#### 1.2.6 K28.1 Swapper Logic

The K28.1 swapper module receives 10-bit code group from the InterSymbol RD swapper module. It undoes the modification done in the transmit path by replacing every occurrence of K28.1 with K28.5 symbol code. Every occurrence of K28.1 in IDLE /I/ and configuration /C/ ordered sets is replaced with K28.5.

The following table lists the K28.1 Swapper definition for Port 0.

Table 1-2. Port0 K28.1 Swapper Definition

| Code | Ordered_Set     | Number of Code<br>Groups | Port 0 "Pre-Swapper" Encoding | Port 0 "Post-Swapper"<br>Encoding |

|------|-----------------|--------------------------|-------------------------------|-----------------------------------|

| /C/  | Configuration   | _                        | Alternating /C1/ and /C2/     | Alternating /C1/ and /C2/         |

| /C1/ | Configuration 1 | 4                        | /K28.1/D21.5/Config_Reg       | /K28.5/D21.5/Config_Reg           |

| /C2/ | Configuration 2 | 4                        | /K28.1/D2.2/Config_Reg        | /K28.5/D2.2/Config_Reg            |

| /1/  | IDLE            | _                        | Correcting /I1/               | Correcting /I1/                   |

| /11/ | IDLE 1          | 2                        | /K28.1/D5.6/                  | /K28.5/D5.6/                      |

## 2. Interface

This section describes the parameters in the CoreQSGMII GUI configurator and I/O signals.

### 2.1 Configuration Parameters

CoreQSGMII has parameters (Verilog) for configuring the RTL code. The following table lists the CoreQSGMII parameters and their description. All parameters are integer types.

Table 2-1. CoreQSGMII Parameters and Generics Descriptions

| Parameter        | Valid Values | Default | Description                 |

|------------------|--------------|---------|-----------------------------|

| MDIO_PHYID_PORT0 | 0–31         | 0       | MDIO PHY address for Port 0 |

| MDIO_PHYID_PORT1 | 0–31         | 1       | MDIO PHY address for Port 1 |

| MDIO_PHYID_PORT2 | 0–31         | 2       | MDIO PHY address for Port 2 |

| MDIO_PHYID_PORT3 | 0–31         | 3       | MDIO PHY address for Port 3 |

### 2.2 I/O Signals

The following table lists the clock port signals for the CoreQSGMII IP.

Table 2-2. CoreQSGMII Clock Signals

| Port Name                                            | Direction | Width | Description                                                                                                         |  |  |  |

|------------------------------------------------------|-----------|-------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| CoreQSGMII Clocks (x represents the range of 0 to 3) |           |       |                                                                                                                     |  |  |  |

| TBI_TX_CLK                                           | 1         | Input | 125 MHz Ten Bit Interface (TBI) transmit clock from transceiver.                                                    |  |  |  |

| TXCLK_Px                                             | 1         | Input | 2.5/25/125 MHz transmit clock generated from transceiver TX clock according to 10/100/1000 Mbps support for port x. |  |  |  |

| TBI_RX_CLK                                           | 1         | Input | 125 MHz TBI receive clock from transceiver.                                                                         |  |  |  |

| RXCLK_Px                                             | 1         | Input | 2.5/25/125 MHz receive clock generated from transceiver RX clock according to 10/100/1000 Mbps support for port x.  |  |  |  |

| MDC                                                  | 1         | Input | Management data clock, recommended to drive 2.5 MHz.                                                                |  |  |  |

The following table describes the input/output ports of the CoreQSGMII IP.

Table 2-3. CoreQSGMII Input/Output Ports

| Port Name | Direction  | Clock Domain   | Width    | Description                                                                                             |  |  |  |

|-----------|------------|----------------|----------|---------------------------------------------------------------------------------------------------------|--|--|--|

|           | Reset Port |                |          |                                                                                                         |  |  |  |

| RESET     | Input      | Asynchronous   | 1        | Asynchronous active high reset. The reset is internally synchronized with the respective clock domains. |  |  |  |

|           |            | G/MII Interfac | ce (x re | presents the range of 0 to 3)                                                                           |  |  |  |

| TXD_x     | Input      | TXCLK_Px       | 8        | G/MII transmit data                                                                                     |  |  |  |

| TXEN_x    | Input      | TXCLK_Px       | 1        | G/MII transmit enable                                                                                   |  |  |  |

| TXER_x    | Input      | TXCLK_Px       | 1        | G/MII transmit error                                                                                    |  |  |  |

| continued    | continued                                            |              |          |                                                     |  |  |

|--------------|------------------------------------------------------|--------------|----------|-----------------------------------------------------|--|--|

| Port Name    | Direction                                            | Clock Domain | Width    | Description                                         |  |  |

| RXD_x        | Output                                               | RXCLK_Px     | 8        | G/MII receive data                                  |  |  |

| RXDV_x       | Output                                               | RXCLK_Px     | 1        | G/MII receive data valid                            |  |  |

| RXER_x       | Output                                               | RXCLK_Px     | 1        | G/MII receive error                                 |  |  |

| COL_x        | Output                                               | RXCLK_Px     | 1        | MII collision                                       |  |  |

| CRS_x        | Output                                               | RXCLK_Px     | 1        | MII carrier sense                                   |  |  |

|              | Ten-Bit Interface (x represents the range of 0 to 3) |              |          |                                                     |  |  |

| TCG_x        | Output                                               | TBI_TX_CLK   | 1        | TBI Transmit Code Group (TCG) for port x            |  |  |

| RCG_x        | Input                                                | TBI_RX_CLK   | 1        | TBI Receive Code Group (RCG) for port x             |  |  |

|              |                                                      | Othe         | er Ten-E | Bit Interface Signals                               |  |  |

| TBI_RX_READY | Input                                                | Asynchronous | 1        | RCG ready, recommended to connect with transceiver. |  |  |

| TBI_RX_VALID | Input                                                | Asynchronous | 1        | RCG valid, recommended to connect with transceiver. |  |  |

|              |                                                      |              | MD       | O Interface                                         |  |  |

| MDO          | Input                                                | MDC          | 1        | Management data output                              |  |  |

| MDOEN        | Input                                                | MDC          | 1        | Management data output enable                       |  |  |

| MDI_EXT      | Input                                                | MDC          | 1        | Management data input from external PCS/PHY         |  |  |

| MDI          | Output                                               | MDC          | 1        | MII Management data Input                           |  |  |

## 3. Register Map and Descriptions

The following table lists the registers that are accessed through the MDIO interface, Clause 22 of the IEEE 802.3 specification. The PHY address for the MDIO registers is configurable. The CoreQSGMII contains the management registers specified in IEEE 802.3, Clause 37. The register set is read/write through MDIO interface.

Prefix 0x represents hex value and 0b represents binary value in the following register summary and register description tables.

Type columns in the register's tables indicate the access type of the registers. The following table describes the access type.

Table 3-1. Access Type Descriptions

| Access Type | Description   |

|-------------|---------------|

| RW          | Read or Write |

| RO          | Read only     |

| ROC         | Read on clear |

Some register's bits may support different access type. All the supported access types are shown under Type column for those registers. All the reserved bits are always read as zero and reserved bits must always be written to zero if accessed unless otherwise specified.

#### 3.1 **Register Summary**

The following table lists the register summary of CoreQSGMII.

Table 3-2. CoreQSGMII Register Summary

| Address | Register Name | Туре      | Width | Reset Value | Description                                |

|---------|---------------|-----------|-------|-------------|--------------------------------------------|

| 0x00    | CTRL          | R/W       | 16    | 0x0000      | Control Register                           |

| 0x01    | STS           | RO        | 16    | 0x0149      | Status Register                            |

| 0x04    | AN_ADV        | R/W       | 16    | 0x0000      | AN Advertisement Register                  |

| 0x05    | AN_LNKPGABL   | RO        | 16    | 0x0000      | AN Link Partner Base Page Ability Register |

| 0x06    | AN_EXPNSN     | RO<br>ROC | 16    | 0x0004      | AN Expansion Register                      |

| 0x07    | AN_NPTX       | R/W<br>RO | 16    | 0x0000      | AN Next Page Transmit Register             |

| 0x08    | AN_LNKABLNXP  | RO        | 16    | 0x0000      | AN Link Partner Ability Next Page Register |

| 0x0F    | EXT_STS       | RO        | 16    | 0xA000      | Extended Status Register                   |

| 0x10    | JTR_DIGN      | R/W       | 16    | 0x0000      | Jitter Diagnostics Register                |

| 0x11    | TBI_CTRL      | R/W       | 16    | 0x0008      | TBI Control Register                       |

#### 3.2 **CoreQSGMII Register Descriptions**

This section describes the register's functionalities.

#### 3.2.1 **Control Register**

This register provides controls bits for the PHY and auto-negotiation process. The following table lists the control register descriptions.

Table 3-3. Control Register

| Address | Register Name | Туре | Width | Reset Value | Description      |

|---------|---------------|------|-------|-------------|------------------|

| 0x00    | CTRL          | R/W  | 16    | 0x0000      | Control Register |

The following table lists the control register bit definitions.

Table 3-4. Control Register Bit Definitions

| Bits | Name     | Туре | Reset Value | Description                                                                                                                                                         |

|------|----------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | PHY_RST  | R/W  | 0           | PHY Reset Setting this bit causes the TEX, REX, and ANX sub-modules in the CoreQSGMII core to be reset. This bit is self-cleared by the IP.                         |

| 14   | LPBK_EN  | R/W  | 0           | Loopback Enbale Setting this bit causes the transmit output of the CoreQSGMII to be connected to the receive inputs. Clearing this bit results in normal operation. |

| 13   | Reserved |      |             |                                                                                                                                                                     |

DS50003421A-page 11 **User Guide** © 2022 Microchip Technology Inc.

|       | continued |          |             |                                                                                                                                                                                                     |  |  |  |  |  |

|-------|-----------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bits  | Name      | Туре     | Reset Value | Description                                                                                                                                                                                         |  |  |  |  |  |

| 12    | AN_EN     | R/W      | 0           | Auto-Negotiation Enable Setting this bit enables the auto-negotiation process.                                                                                                                      |  |  |  |  |  |

| 11:10 | Reserved  |          |             |                                                                                                                                                                                                     |  |  |  |  |  |

| 9     | AN_RSTRT  | R/W      | 0           | Restart Auto-Negotiation Setting this bit causes the auto negotiation process to restart. This action is only available when Auto-Negotiation has been enabled. This bit is self-cleared by the IP. |  |  |  |  |  |

| 8:0   | Reserved  | Reserved |             |                                                                                                                                                                                                     |  |  |  |  |  |

### 3.2.2 Status Register

This register provides PHY status, auto-negotiation process status and link status. The following table lists the status register descriptions.

Table 3-5. Status Register

| Address | Register Name | Туре | Width | Reset Value | Description     |

|---------|---------------|------|-------|-------------|-----------------|

| 0x01    | STS           | RO   | 16    | 0x0149      | Status Register |

The following table lists the status register bit definitions.

Table 3-6. Status Register Bit Definitions

| Bits | Name              | Туре | Reset<br>Value | Description                                                                                                                                    |  |  |  |  |  |

|------|-------------------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 15:9 | Reserved          |      |                |                                                                                                                                                |  |  |  |  |  |

| 8    | EXTND_STS         | RO   | 1              | Extended Status This bit indicates that PHY status information is also contained in extended status register.                                  |  |  |  |  |  |

| 7    | Reserved          |      |                |                                                                                                                                                |  |  |  |  |  |

| 6    | PRMBLE_SUPPRES_EN | RO   | 1              | Preamble Suppression Enable This bit indicates whether the PHY is capable of handling MII management frames without the 32-bit preamble field. |  |  |  |  |  |

|      |                   |      |                | Returns 1 to indicate support for suppressing preamble MII management frames.                                                                  |  |  |  |  |  |

| 5    | AN_CMPL           | RO   | 0              | Auto-Negotiation Complete When 1, this bit indicates that the auto-negotiation process has completed.                                          |  |  |  |  |  |

|      |                   |      |                | This bit returns '0' when either the auto-negotiation process is in progress, or the auto-negotiation function is disabled.                    |  |  |  |  |  |

| 4    | RMT_FAULT         | RO   | 0              | Remote Fault Assertion of this bit indicates that remote fault condition has been detected between the CoreQSGMII and the PHY.                 |  |  |  |  |  |

| 3    | AN_ABL            | RO   | 1              | Auto Negotiation Ability Assertion of this bit indicates that the CoreQSGMII can perform auto-negotiation.                                     |  |  |  |  |  |

© 2022 Microchip Technology Inc. User Guide DS50003421A-page 12

|      | continued |      |                |                                                                                                                                                                                                     |  |  |  |  |  |

|------|-----------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bits | Name      | Туре | Reset<br>Value | Description                                                                                                                                                                                         |  |  |  |  |  |

| 2    | LINK_STS  | RO   | 0              | Link Status Assertion of this bit indicates that a valid link has been established between the CoreQSGMII and the PHY.  De-assertion of this bit indicates that no valid link has been established. |  |  |  |  |  |

| 1    | Reserved  |      |                |                                                                                                                                                                                                     |  |  |  |  |  |

| 0    | EXTND_CAP | RO   | 1              | Extended Capability Assertion of this bit indicates that the CoreQSGMII contains the extended set of registers.                                                                                     |  |  |  |  |  |

### 3.2.3 AN Advertisement Register

This register provides configuration of local device ability during auto-negotiation operation with PHY. The following table lists the auto-negotiation advertisement register descriptions.

Table 3-7. AN Advertisement Register

| Address | Register Name | Туре | Width | Reset Value | Description               |

|---------|---------------|------|-------|-------------|---------------------------|

| 0x04    | AN_ADV        | R/W  | 16    | 0x0000      | AN Advertisement Register |

The following table lists the auto-negotiation advertisement register bit definitions.

Table 3-8. AN Advertisement Register Bit Definitions

| Bits  | Name                     | Туре        | Reset Value  | Description                                                                                                                                                        |                                      |  |  |  |  |

|-------|--------------------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| AN Ac | AN Advertisement - SGMII |             |              |                                                                                                                                                                    |                                      |  |  |  |  |

| 15:13 | Reserved                 |             |              |                                                                                                                                                                    |                                      |  |  |  |  |

| 12    | FDUPLX                   | R/W         | 0            | Full-Duplex The assertion of this bit indicates the full-duplex mode.                                                                                              | nat the link is transferring data in |  |  |  |  |

| 11:10 | LSPEED                   | ED R/W 0b00 | 0b00         | Link Speed Link speed set by the application for the auto-negotiation. For link speed encoding, see the following table speed.  Table 3-9. Link Speed Descriptions |                                      |  |  |  |  |

|       |                          |             |              | Bits [11:10]                                                                                                                                                       | Speed                                |  |  |  |  |

|       |                          |             |              | 00                                                                                                                                                                 | 10 Mbps                              |  |  |  |  |

|       |                          |             |              | 01                                                                                                                                                                 | 100 Mbps                             |  |  |  |  |

|       |                          |             |              | 10                                                                                                                                                                 | 1000 Mbps                            |  |  |  |  |

|       |                          |             |              | 11                                                                                                                                                                 | Reserved                             |  |  |  |  |

| 9:0   | RSVD                     | R/W         | 060000000000 | Reserved As per the SGMII specification this 0x000000001.                                                                                                          | register must be written to          |  |  |  |  |

| AN Ac | lvertisement - 1         | 000BA       | SE-X         | ı                                                                                                                                                                  |                                      |  |  |  |  |

© 2022 Microchip Technology Inc. User Guide DS50003421A-page 13

|       | continued            |      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                |              |                                                                                                   |

|-------|----------------------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------------|---------------------------------------------------------------------------------------------------|

| Bits  | Name                 | Туре | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                |              |                                                                                                   |

| 15    | NXTPG                | R/W  | 0           | Next Page The local device asserts this bit to either request Next Page transmission or advertise next page exchange capability. This bit is set when the local has no Next Pages but wishes to allow reception of Next Pages. If the local device has no Next Pages, and the link partner wishes to send Next Pages, the local device must send null message codes and have the MESSAGE PAGE set to 0b000_0000_0001. This bit must be cleared where the local device wishes not to engage in Next Page exchange. |                   |                |              |                                                                                                   |

| 14    | Reserved             | '    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                |              |                                                                                                   |

| 13:12 | 13:12 RMTFLT_ENC R/V | R/W  | 0b00        | be indicated by s<br>negotiating. For                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | setting<br>remote | a non<br>fault | zero<br>enco | e fault condition. A fault may<br>Remote Fault encoding and re-<br>ding, see the following table. |

|       |                      |      |             | Table 3-10. Rem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                | ncoai        | _                                                                                                 |

|       |                      |      |             | RF1(4,12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RF2(              | 4,13)          |              | Description                                                                                       |

|       |                      |      |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                 |                |              | No error, link ok                                                                                 |

|       |                      |      |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                 |                |              | Offline                                                                                           |

|       |                      |      |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                 |                |              | Link failure                                                                                      |

|       |                      |      |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                 |                |              | Auto negotiation error                                                                            |

| 11:9  | Reserved             |      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                |              |                                                                                                   |

| 8:7   | PAUS_ABL             | R/W  | 0b00        | Pause Ability Encodes the local device's PAUSE capability. For pause encoding, see the following table.                                                                                                                                                                                                                                                                                                                                                                                                           |                   |                |              |                                                                                                   |

|       |                      |      |             | Table 3-11. Paus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e Enc             | oding          | I            |                                                                                                   |

|       |                      |      |             | Pause(4,7) ASM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /I_DIR            | (4,8)          | Cap          | pability                                                                                          |

|       |                      |      |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | 0              | No           | pause                                                                                             |

|       |                      |      |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | 1              | Asy          | mmetric pause toward link<br>ner                                                                  |

|       |                      |      |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | 0              | Syn          | nmetric pause                                                                                     |

|       |                      |      |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | 1              | Asy<br>dev   | mmetric pause toward local<br>ice                                                                 |

| 6     | HDUPLX               | R/W  | 0           | Half-Duplex<br>Setting this bit to<br>operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | o 1 indi          | cates          | local        | device is capable of half-duplex                                                                  |

| 5     | FDUPLX               | R/W  | 0           | Full-Duplex Setting this bit to 1 indicates local device is capable of half-duplex operation.                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |                |              |                                                                                                   |

| 4:0   | Reserved             |      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                |              |                                                                                                   |

#### 3.2.4 AN Link Partner Base Page Ability Register

This register provides details of PHY ability received during auto negotiation process. The following table lists the auto-negotiation link partner base page ability register descriptions.

Table 3-12. AN Link Partner Base Page Ability Register

| Address | Register Name | Туре | Width | Reset Value | Description                                |

|---------|---------------|------|-------|-------------|--------------------------------------------|

| 0x05    | AN_LNKPGABL   | RO   | 16    | 0x0000      | AN Link Partner Base Page Ability Register |

The following table lists the auto-negotiation link partner base page ability register definitions.

Table 3-13. AN Link Partner Base Page Ability Register Bit Definitions

| Bits  | Name                                  | Туре   | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |  |  |

|-------|---------------------------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| AN Li | ink Partner Base Page Ability - SGMII |        |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |  |  |

| 15    | LNKUP                                 | RO     | 0              | Link Up Status<br>Assertion of this bit indicates that t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | he link is up.                   |  |  |

| 14:13 | Reserved                              |        |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |  |  |

| 12    | LP_FDUPLX                             | RO     | 0              | Link Partner Full Duplex Ability<br>Assertion of this bit indicates that li<br>data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ink partner supports full duplex |  |  |

| 11:10 | LP_LSPEED                             | RO     | 0b00           | Link Partner Link Speed Ability These two bits indicates the link papartner speed encoding, see the for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |  |  |

|       |                                       |        |                | Table 3-14. Link Parter Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |  |  |

|       |                                       |        |                | Bits[11:10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Speed                            |  |  |

|       |                                       |        |                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 Mbps                          |  |  |