# Full-Bridge or Single-Ended Audio Amplifier **Evaluation Board**

#### **DESCRIPTION**

The EV8040-N-00A is an evaluation board designed to demonstrate the capabilities of MPS's MP8040. It can be configured as a stereo single-ended amplifier or a full-bridge mono amplifier.

The MP8040 is a general purpose, highfrequency, half-bridge power driver. It integrates both top and bottom N-channel MOSFET power switches. It interfaces with standard logic signals, and is available in small, 8-lead SOIC package.

## **ELECTRICAL SPECIFICATION**

| Parameter            | Symbol                | Value     | Units |

|----------------------|-----------------------|-----------|-------|

| Input supply voltage | V <sub>IN</sub>       | 7.5 to 24 | V     |

| Peak output current  | I <sub>PEAK-MAX</sub> | 9         | Α     |

| RMS output current   | I <sub>RMS-MAX</sub>  | 4.25      | Α     |

#### **FEATURES**

- Up to 1.2MHz Switching Frequency

- Protected Integrated Power 0.1Ω Switches

- Designed Switch Dead time of 30ns

- All Switches Current Limited

- Internal Under-Voltage Protection (UVP)

- o Internal Thermal Protection

- 2.5µA Standby Mode

- **Fault Indicator Output**

# **APPLICATIONS**

- Full or Half-Bridge DC/DC Switching Regulators

- Class-D Audio Drivers

- Motor Drivers

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

#### **EV8040-N-00A EVALUATION BOARD**

(LxWxH) 8.89cmx9.14cmx3cm

| Board Number | MPS IC Number |  |

|--------------|---------------|--|

| EV8040-N-00A | MP8040DN      |  |

## **QUICK START GUIDE**

- 1. The EV8040-N-00A can be configured as a stereo single-ended audio amplifier.

- 2. To configure the board as a full-bridge circuit, short R4, R7, and R9. Then remove C4 and C7. Lastly, use a 0.47µF capacitor for C12.

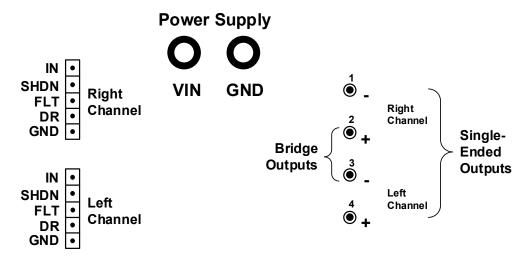

- 3. Connect the audio inputs to the IN pins (see Figure 1).

- 4. Connect speakers to pins 1, 2, 3, and 4 for single-ended configuration (see Figure 1). Use pins 2 and 3 to form a bridged circuit.

- 5. Connect the power supply to the VIN terminals (see Figure 1).

- 6. SHDN enables/disables the MP8040. Drive SHDN low to turn the MP8040 on; drive SHDN high to turn the device off. If SHDN is not used, connect it to GND.

- A low output at FLT indicates that the MP8040 has detected a fault, and the device shuts down as a result.

- 8. The DR pin is an optional, 5V fixed-voltage output capable of driving a 1mA load for external circuitry.

Figure 1: Top-Side Evaluation Board Diagram

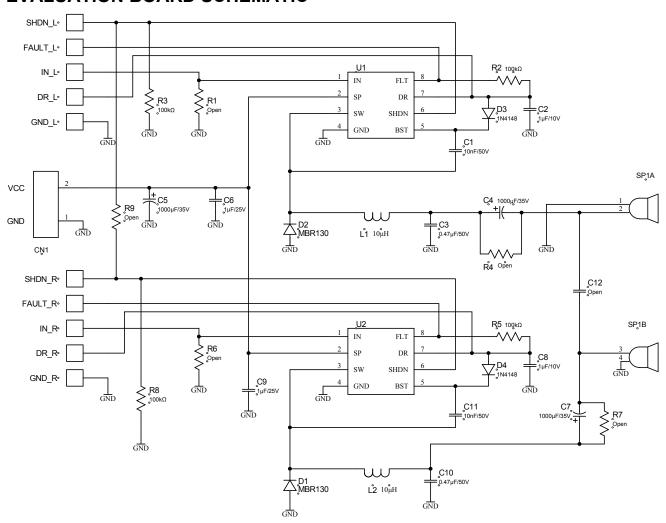

# **EVALUATION BOARD SCHEMATIC**

# **EV8040-N-00A BILL OF MATERIALS**

| Qty | Ref                                                                   | Value          | Description                            | Package   | Manufacturer        | Manufacturer P/N   |

|-----|-----------------------------------------------------------------------|----------------|----------------------------------------|-----------|---------------------|--------------------|

| 2   | U1, U2                                                                | 24V,<br>4.25A  | PWM power driver                       | SOIC-8N   | MPS                 | MP8040DN           |

| 3   | C4, C5,<br>C7                                                         | 1000µF         | Electrolytic<br>capacitor, 35V,<br>DIP | 12.5 x 20 | Jiang Hai           | CD263-35V1000      |

| 3   | C3, C10                                                               | 0.47µF         | Film capacitor,<br>50V                 | 5.08      | Panasonic           | ECQV1H474JL        |

| 2   | C1, C11                                                               | 10nF           | Ceramic<br>capacitor, 50V,<br>NPO/X7R  | 0603      | murata              | GRM188R71H103KA01D |

| 2   | C2, C8                                                                | 1µF            | Ceramic<br>capacitor, 10V,<br>X7R      | 0805      | murata              | GRM21BR71A105KA01L |

| 2   | C6, C9                                                                | 1µF            | Ceramic<br>capacitor, 25V,<br>X7R      | 1206      | murata              | GRM31MR71E105KA01  |

| 2   | L1, L2                                                                | 10µH           | 10μH, 5A,<br>inductor                  | DIP       | wurth               | 7447471100         |

| 4   | R2, R3,<br>R5, R8                                                     | 100kΩ          | 5% resistor                            | 0805      | Yageo               | RC0805JR-07100KL   |

| 2   | D1, D2                                                                | 1A,30V         | 1A, 30V,<br>Schottky rectifier         | SMB       | On<br>Semiconductor | MBRS130T3G         |

| 2   | D3, D4                                                                | 300mA,<br>100V | 300mA, 100V, rectifier                 | SOD123    | Diodes Inc.         | 1N4148WS           |

| 10  | IN_L, SHDN_L, FAULT_L, DR_L, GND_L, IN_R, SHDN_R FAULT_R, DR_R, GND_R | 2.54mm         | 2.54mm<br>Connector                    | DIP       | Electrical Market   | 61304011121        |

| 4   | SP1                                                                   | Φ =<br>1mm     | 1mm connector                          | DIP       | Electrical Market   | Φ = 1mm Needle     |

| 2   | CN1                                                                   | Φ =<br>2mm     | 2mm connector                          | DIP       | Electrical Market   | Φ = 2mm Needle     |

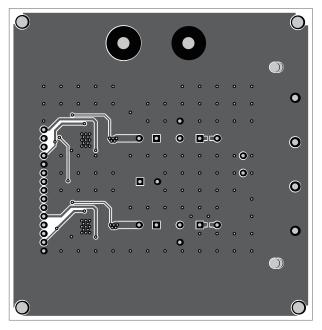

## **PCB LAYOUT**

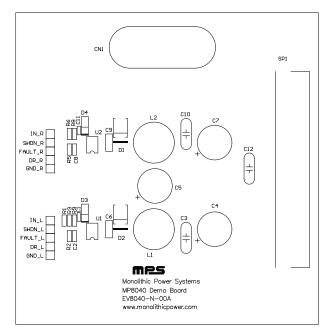

Figure 2: Top Silk Layer

Figure 3: Top Layer

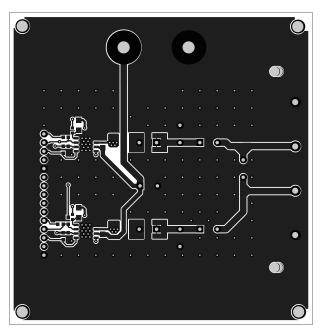

Figure 4: Bottom Layer

Notice: The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.