# EVBL4423H-Q-00A

36V, 3A, Synchronous, Step-Down Converter Evaluation Board

#### **DESCRIPTION**

The EVBL4423H-Q-00A is an evaluation board designed to demonstrate the MP4423H and the MPQ4423H. The MP4423H is a high-frequency, synchronous, rectified, step-down switch-mode converter with built-in power MOSFETs and an integrated MPS power inductor. It offers a compact solution that can achieve up to 3A of continuous output current ( $I_{OUT}$ ) across a wide 4V to 36V input voltage ( $V_{IN}$ ) range, with excellent load and line regulation.

Synchronous mode provides high efficiency across the entire  $I_{\text{OUT}}$  range. Current-mode control provides fast transient response and eases loop stabilization.

Full protection features include over-current protection (OCP) with hiccup mode and thermal shutdown.

The EVBL4423H-Q-00A is a fully assembled and tested evaluation board. The MP4423H is available in a QFN-8 (3mmx3mm) package.

#### **ELECTRICAL SPECIFICATIONS**

| Parameter      | Symbol           | Value   | Units |

|----------------|------------------|---------|-------|

| Input voltage  | $V_{IN}$         | 4 to 36 | V     |

| Output voltage | V <sub>OUT</sub> | 3.3     | V     |

| Output current | I <sub>OUT</sub> | 3       | Α     |

#### **FEATURES**

- Wide 4V to 36V Operating Input Voltage (V<sub>IN</sub>) Range

- $85m\Omega/55m\Omega$ , Low  $R_{DS(ON)}$  Internal Power MOSFETs

- High-Efficiency Synchronous Mode

- 410kHz Default Switching Frequency (f<sub>SW</sub>)

- 200kHz to 2.2MHz Synchronized External Clock

- High Duty Cycle for Automotive Cold-Crank Conditions

- Power-Save Mode (PSM)

- Internal Soft Start (SS)

- Power Good (PG)

- Over-Current Protection (OCP) with Hiccup Mode

- Thermal Shutdown

- Fully Assembled and Tested

- Available in a QFN-8 (3mmx3mm) Package

- Available in AEC-Q100 Grade 1

-MPL

Optimized Performance with MPS Inductor MPL-AL6060 Series

#### **APPLICATIONS**

- Automotive Applications

- Industrial Control Systems

- Distributed Power Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

# **EVBL4423H-Q-00A EVALUATION BOARD**

LxWxH (6.35cmx6.35cmx0.5cm)

| Board<br>Number | MPS IC<br>Number | MPS<br>Inductor |  |

|-----------------|------------------|-----------------|--|

| EVBL4423H-      | MP4423HGQ,       | MPL-            |  |

| Q-00A           | MPQ4423HGQ       | AL6060-100      |  |

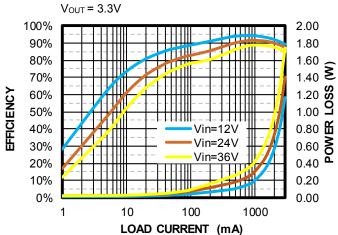

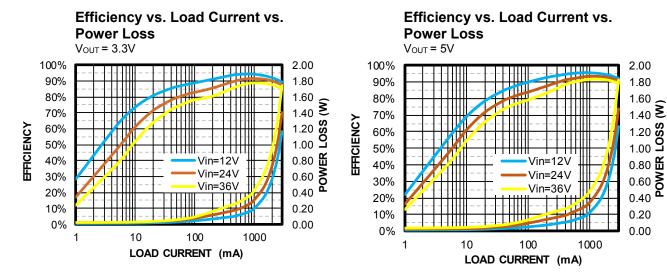

# Efficiency vs. Load Current vs. Power Loss

#### QUICK START GUIDE

- 1. Connect the load terminals to:

- a. Positive (+): VOUT

- b. Negative (-): GND

- 2. Preset the power supply between 4V and 36V, then turn the power supply off.

- 3. Connect the power supply terminals to:

- a. Positive (+): VIN

- b. Negative (-): GND

- 4. Turn the power supply on. The evaluation board should start up automatically.

- 5. To use the enable (EN) function, apply a digital input to the EN/SYNC pin. Pull EN/SYNC above 1.65V to turn the converter on; pull EN/SYNC below 1.05V or float EN/SYNC to turn it off. Connect an internal 500k $\Omega$  resistor between the EN/SYNC and GND pins to allow EN/SYNC to be floated.

- 6. Connect the EN/SYNC input pin to any voltage connected to the VIN pin via a pull-up resistor (R1). Ensure that R1 is large enough to limit the EN input current below 150µA. For example, if EN/SYNC is connected to a 12V  $V_{IN}$ , then R1 should be  $\geq$ 36.7k $\Omega$ .

- 7. To connect EN/SYNC directly to a voltage source without using a pull-up resistor, the voltage amplitude should be limited to ≤6V to prevent damage to the internal Zener diode at EN/SYNC.

- 8. After the output voltage (V<sub>OUT</sub>) is set, connect the EN/SYNC input pin to a 200kHz to 2.2MHz external clock to synchronize the internal clock's rising edge to the external clock's rising edge. The external clock's pulse-width signal should be below 1.7µs.

- 9. Use R7 and R8 to set V<sub>OUT</sub>. R8 can be calculated by Equation (1):

$$R8 = \frac{R7}{\frac{V_{OUT}}{0.792} - 1} \tag{1}$$

Where R7 is  $41.2k\Omega$ , and  $V_{FB}$  is 0.792V.

If V<sub>OUT</sub> is changed, refer to the Application Information section in the MP4423H/MPQ4423H datasheet to calculate the compensation, inductance, and output capacitance.

10. CLK OUT is a signal inverted to SW that can be used as another buck's SYNC signal to operate 180° out-of-phase. The CLK OUT high voltage is equal to V<sub>OUT</sub>. Ensure that it is safe to operate the synchronized part while V<sub>OUT</sub> is high.

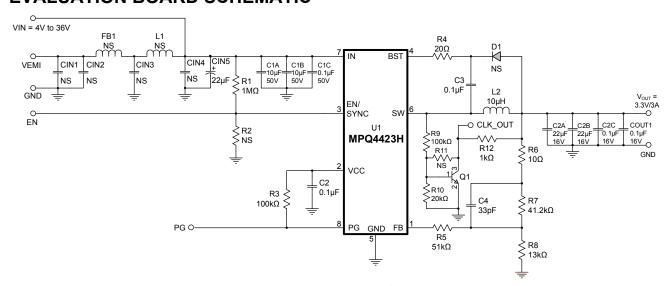

# **EVALUATION BOARD SCHEMATIC**

Figure 1: Evaluation Board Schematic

© 2021 MPS. All Rights Reserved.

4

# **EVBL4423H-Q-00A BILL OF MATERIALS**

| Qty | Ref                                     | Value                  | Description                       | Package                | Manufacturer        | Manufacturer PN    |

|-----|-----------------------------------------|------------------------|-----------------------------------|------------------------|---------------------|--------------------|

| 2   | C1A, C1B                                | 10μF                   | Ceramic capacitor,<br>50V, X7R    | 1210                   | Murata              | GRM32ER71H106KA12L |

| 1   | C1C                                     | 0.1µF                  | Ceramic capacitor, 50V, X7R       | 0603                   | Murata              | GRM188R71H104KA93D |

| 2   | C2A, C2B                                | 22µF                   | Ceramic capacitor,<br>16V, X7R    | 1210                   | Murata              | GRM32ER71C226KE79  |

| 4   | C2, C2C,<br>C3, COUT1                   | 0.1µF                  | Ceramic capacitor,<br>16V, X7R    | 0603                   | Murata              | GRM188R71C104KA01D |

| 1   | C4                                      | 33pF                   | Ceramic capacitor, 50V, C0G       | 0603                   | Murata              | GRM1885C1H330JA01D |

| 4   | CIN1,<br>CIN2,<br>CIN3, CIN4            | NS                     |                                   |                        |                     |                    |

| 1   | CIN5                                    | 22µF                   | Electrolytic capacitor            | SMD                    | Jianghai            | VTD-63V22          |

| 1   | D1                                      | NS                     |                                   |                        |                     |                    |

| 1   | FB1                                     | NS                     |                                   |                        |                     |                    |

| 1   | L1                                      | NS                     |                                   |                        |                     |                    |

| 1   | R1                                      | 1ΜΩ                    | Film resistor, 5%                 | 0603                   | Yageo               | RC0603JR-071ML     |

| 2   | R3, R9                                  | 100kΩ                  | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-07100KL   |

| 1   | R4                                      | 20Ω                    | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-0720RL    |

| 1   | R5                                      | 51kΩ                   | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-0751KL    |

| 1   | R6                                      | 10Ω                    | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-0710RL    |

| 1   | R7                                      | 41.2kΩ                 | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-0741K2L   |

| 1   | R8                                      | 13kΩ                   | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-0713KL    |

| 1   | R10                                     | 20kΩ                   | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-0720KL    |

| 1   | R12                                     | 1kΩ                    | Film resistor, 1%                 | 0603                   | Yageo               | RC0603FR-071KL     |

| 2   | R2, R11                                 | NS                     |                                   |                        |                     |                    |

| 5   | VIN, VEMI,<br>GND,<br>VOUT,<br>GND      | 2mm                    | 2mm golden test pin               | DIP                    | Custom (1)          |                    |

| 5   | EN/SYNC,<br>GND,<br>PG ,GND,<br>CLK_OUT | 1mm                    | 1mm golden pin                    | DIP                    | Custom (1)          |                    |

| 1   | Q1                                      | 40V                    | Transistor, 0.2A                  | SOT-23                 | ON<br>Semiconductor | MMBT3904LT1        |

| 1   | L2                                      | MPL-<br>AL6060-<br>100 | Inductor, 10μH, 7A,<br>DCR = 27mΩ | SMD                    | MPS                 | MPL-AL6060-100     |

| 1   | U1                                      | MPQ4423H               | Step-down converter, 36V, 3A      | QFN-8<br>(3mmx<br>3mm) | MPS                 | MPQ4423HGQ         |

#### Note:

<sup>1)</sup> These pins are custom-made by MPS. Contact an MPS FAE for more information.

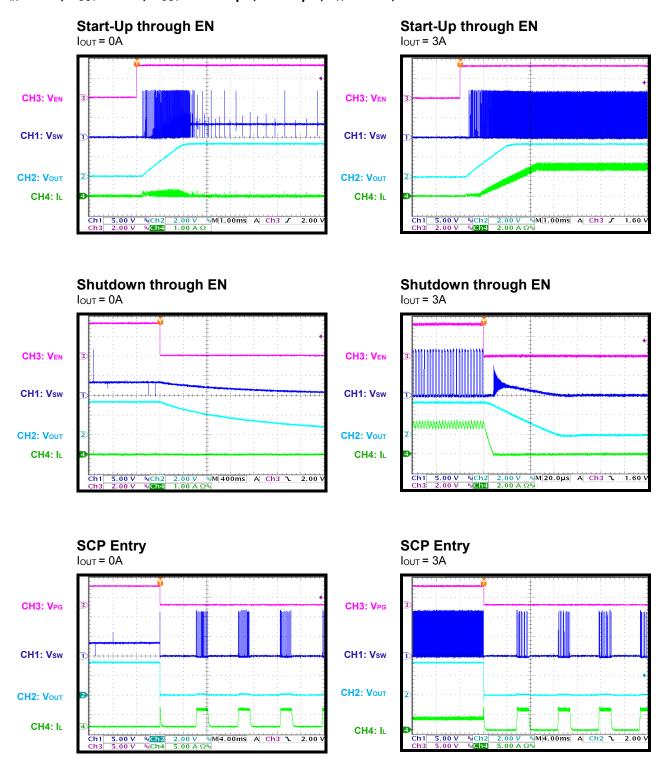

#### **EVB TEST RESULTS**

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $C_{OUT}$  = 2 x 22 $\mu$ F, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

6

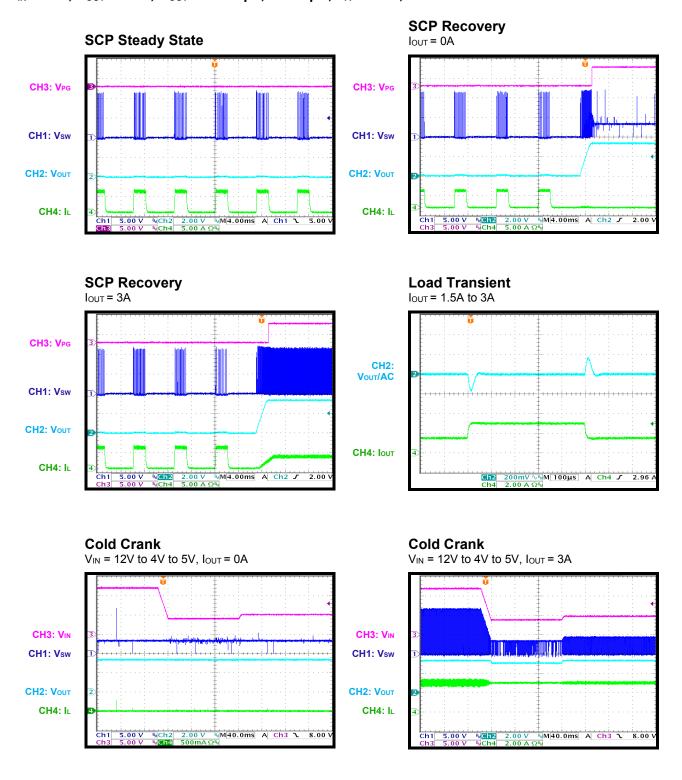

### **EVB TEST RESULTS** (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $C_{OUT}$  = 2 x 22 $\mu$ F, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

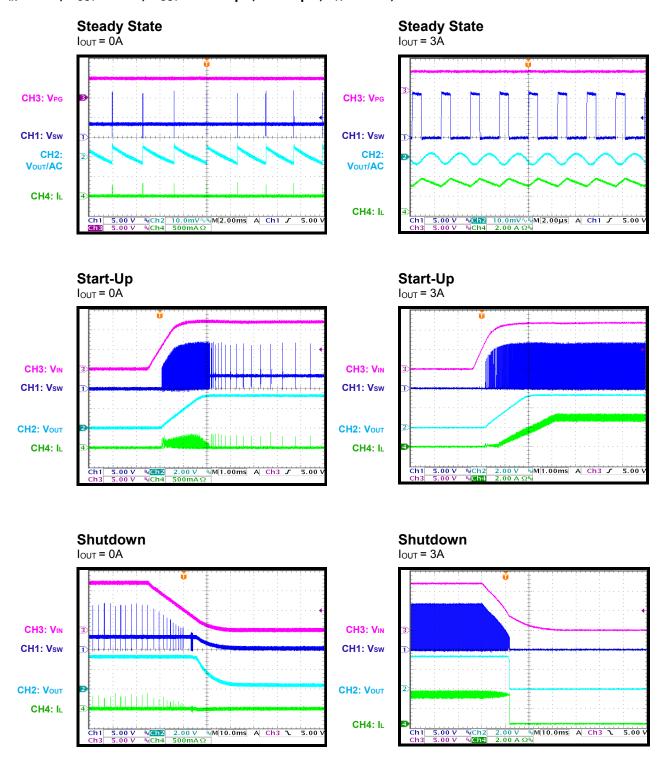

# **EVB TEST RESULTS** (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $C_{OUT}$  = 2 x 22 $\mu$ F, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

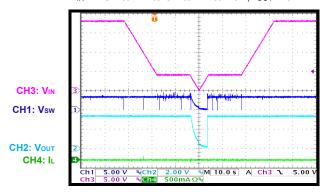

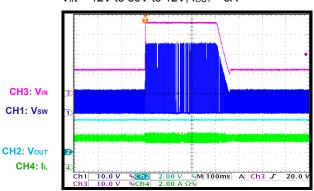

### **EVB TEST RESULTS** (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $C_{OUT}$  = 2 x 22 $\mu$ F, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

CH3: VIN

CH1: Vsw

CH2: Vout

CH4: IL

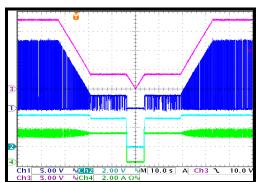

# **EVB TEST RESULTS** (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $C_{OUT}$  = 2 x 22 $\mu$ F, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

#### **V**<sub>IN</sub> Ramps Down and Up

$V_{IN}$  = 18V to 4V to 0V to 4V to 18V,  $I_{OUT}$  = 0A

#### **VIN Ramps Down and Up**

$V_{IN}$  = 18V to 4V to 0V to 4V to 18V,  $I_{OUT}$  = 3A

#### **Load Dump**

$V_{IN}$  = 12V to 36V to 12V,  $I_{OUT}$  = 3A

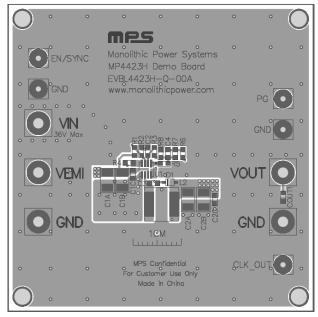

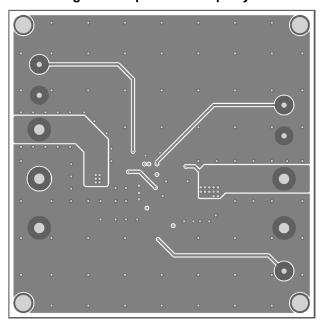

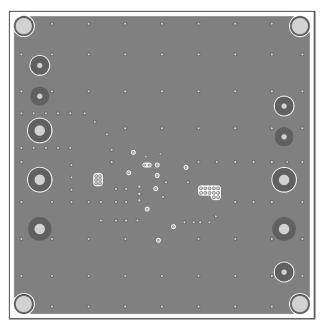

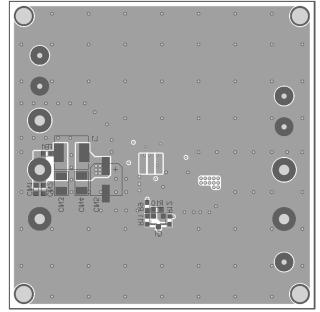

# **PCB LAYOUT**

Figure 2: Top Silk and Top Layer

Figure 4: Mid-Layer 2

Figure 3: Mid-Layer 1

Figure 5: Bottom Silk Layer and Bottom Layer

# EVBL4423H-Q-00A - 36V, 3A SYNC STEP-DOWN CONVERTER EVAL BOARD

# **REVISION HISTORY**

| Revision # | Revision Date | Description                                           | Pages Updated |

|------------|---------------|-------------------------------------------------------|---------------|

| 1.0        | 9/29/2019     | Initial Release                                       | -             |

| 1.1        | 10/21/2021    | Updated the footnote below the Applications section   | 1             |

|            |               | Updated the Quick Start Guide section                 | 2             |

|            |               | Updated the graph and waveform titles in the EVB Test | 6–10          |

|            |               | Results section                                       | 0-10          |

|            |               | Grammar and formatting updates; updated pagination;   | All           |

|            |               | updated figure titles; updated headers                | ΔII           |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.