# PART NUMBER 54161DMB-ROCV

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

T-45-23-05 161 • 163

# 54/74161 • 54LS/74LS161 54/74163 • 54LS/74LS163

### SYNCHRONOUS PRESETTABLE **BINARY COUNTERS**

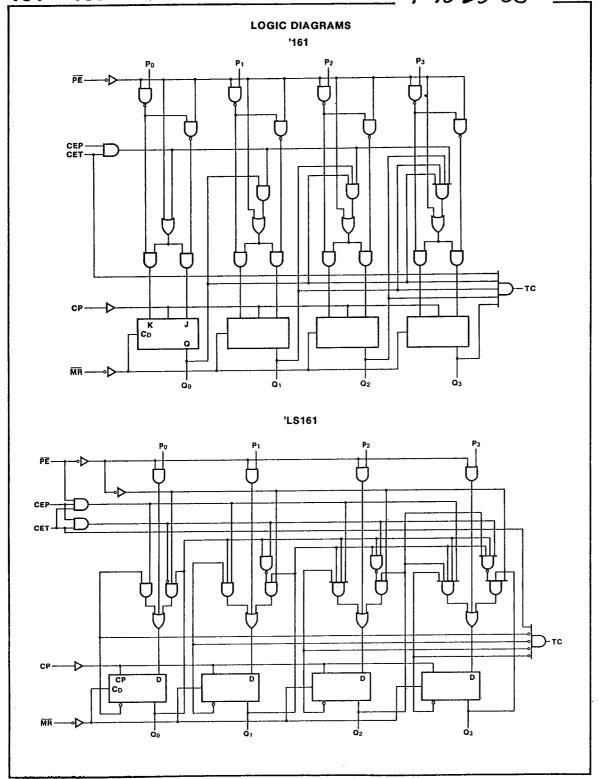

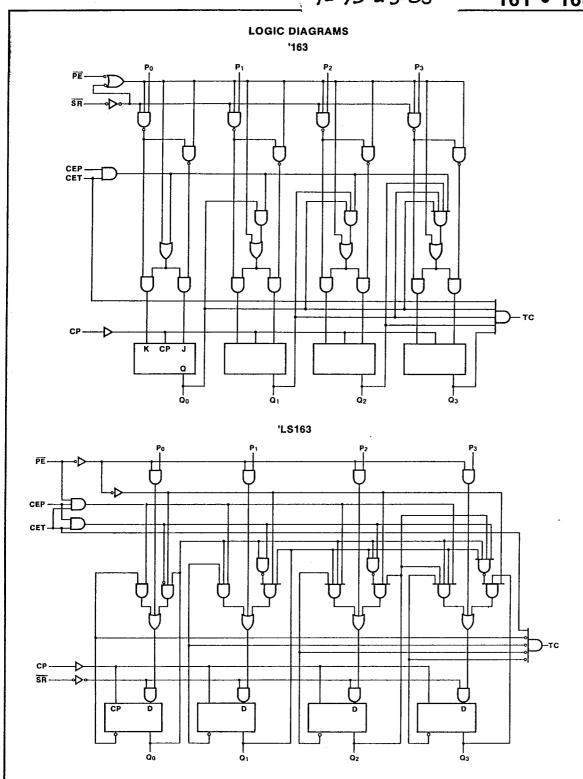

DESCRIPTION - The '161 and '163 are high speed synchronous modulo-16 binary counters. They are synchronously presettable for application in programmable dividers and have two types of Count Enable inputs plus a Terminal Count output for versatility in forming synchronous multistage counters. The '161 has an asynchronous Master Reset input that overrides all other inputs and forces the outputs LOW. The '163 has a Synchronous Reset input that overrides counting and parallel loading and allows the outputs to be simultaneously reset on the rising edge of the clock. For functional description and detail specifications please refer to the '160 data sheet. For S-TTL and LP-TTL versions please see the 9316 data sheet.

- SYNCHRONOUS COUNTING AND LOADING

- HIGH SPEED SYNCHRONOUS EXPANSION

- LS VERSIONS FULLY EDGE TRIGGERED

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                  | PKG  |  |

|--------------------|-----|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|--|

| PKGS               | OUT | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} + 125^{\circ} \text{ C}$ | TYPE |  |

| Plastic<br>DIP (P) | Α   | 74161PC, 74LS161PC<br>74163PC, 74LS163PC                                                 |                                                                                                 | 9В   |  |

| Ceramic<br>DIP (D) | Α   | 74161DC, 74LS161DC<br>74163DC, 74LS163DC                                                 | 54161DM, 54LS161DM<br>54163DM, 54LS163DM                                                        | 7B   |  |

| Flatpak<br>(F)     | Α   | 74161FC, 74LS161FC<br>74163FC, 74LS163FC                                                 | 54161FM, 54LS161FM<br>54163FM, 54LS163FM                                                        | 4L   |  |

#### **CONNECTION DIAGRAM** PINOUT A 16 Vcc 15 TC CP 2 14 Co Po 3 1301 Pt 4 12 02 P2 5 11100 P3 6 10 CET 9 PE \*MR for '161 \*SR for '163

#### LOGIC SYMBOL

\*MR for '161 Vcc = Pin 16 Gnd = Pin 8 \*SR for '163

#### STATE DIAGRAM

INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES     | DESCRIPTION                                  | <b>54/74 (U.L.)</b><br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW |  |

|---------------|----------------------------------------------|---------------------------------|----------------------------|--|

| CEP           | Count Enable Parallel Input                  | 1.0/1.0                         | 0.6/0.3                    |  |

| CET           | Count Enable Trickle Input                   | 2.0/2.0                         | 1.0/0.5                    |  |

| CP            | Clock Pulse Input (Active Rising Edge)       | 2.0/2.0                         | 0.6/0.3                    |  |

| MR ('161)     | Asynchronous Master Reset Input (Active LOW) | 1.0/1.0                         | 0.5/0.25                   |  |

| SR ('163)     | Synchronous Reset Input (Active LOW)         | 1.0/1.0                         | 0.5/0.25                   |  |

| Po — P3       | Parallel Data Inputs                         | 1.0/1.0                         | 0.5/0.25                   |  |

| Po — P3<br>PE | Parallel Enable Input (Active LOW)           | 1.0/1.0                         | 0.6/0.3                    |  |

| $Q_0 - Q_3$   | Flip-flop Outputs                            | 20/10                           | 10/5.0                     |  |

|               |                                              |                                 | (2.5)                      |  |

| ГС            | Terminal Count Output                        | 20/10                           | 10/5.0                     |  |

|               |                                              |                                 | (2,5)                      |  |

4-221 54/6/-/x

าชา ● 163

T-45-23-05

1254

F-03

4-222 54/6/-2x

4-223 54/61-3x

1255

F-04