## PART NUMBER 74167N-ROCS

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## SN54167, SN74167

## Synchronous Decade Rate Multiples

These monolithic, fully synchronous, programmable counters utilize Series 54/74 TTL circuitry to achieve 32-megahertz typical maximum operating frequencies. These decade counters feature buffered clock, clear, enable and set-to-nine inputs to control the operation of the counter, and a strobe input to enable or inhibit the rate input/decoding AND-OR-INVERT gates. The outputs have additional gating for cascading and transferring unity-count rates.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

DECEMBER 1972 - REVISED MARCH 1988

- Perform Fixed-Rate or Variable-Rate Frequency Division

- For Applications in Arithmetic, Radar, Digital-to-Analog (D/A), Analog-to-Digital (A/D), and other Conversion Operations

- Typical Maximum Clock Frequency . . . 32 MHz

#### description

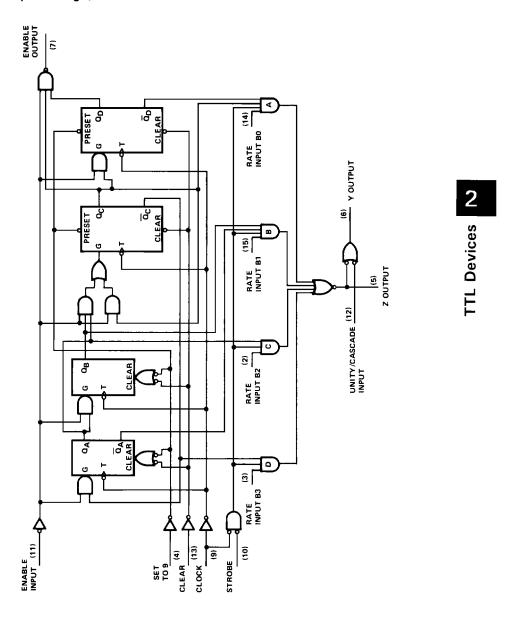

These monolithic, fully synchronous, programmable counters utilize Series 54/74 TTL circuitry to achieve 32-megahertz typical maximum operating frequencies. These decade counters feature buffered clock, clear, enable and set-to-nine inputs to control the operation of the counter, and a strobe input to enable or inhibit the rate input/decoding AND-OR-INVERT gates. The outputs have additional gating for cascading and transferring unity-count rates.

The counter is enabled when the clear, strobe set-to-nine, and enable inputs are low. With the counter enabled, the output frequency is equal to the input frequency multiplied by the rate input M and divided by 10, le.:

$$f_{out} = \frac{M \cdot f_{in}}{10}$$

where:  $M = B3 \cdot 2^3 + B2 \cdot 2^2 + B1 \cdot 2^1 + B0 \cdot 2^0$ for decimal zero through nine.

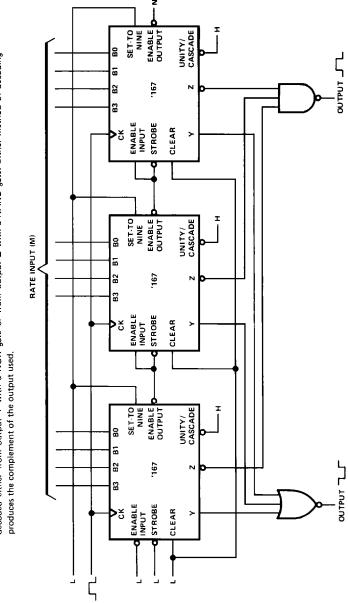

When the rate input is binary 0 (all rate inputs low), Z remains high. In order to cascade devices to perform two-decade rate multiplication (0-99), the enable output is connected to the enable and

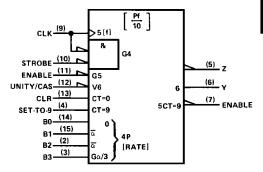

SN54167 . ... J OR W PACKAGE SN74167 . . . N PACKAGE (TOP VIEW) NC □¹ U16 VCC B2 🛮 2 15 Bi B3 🛮 3 14 B0 SET-TO-9 13 CLR **5** 12 UNITY/CAS Z Υ П6 11 ENin **ENout** 10 STRB GND 9 CLK

NC-No internal connection

#### logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

strobe inputs of the next stage, the Z output of each stage is connected to the unity/cascade input of the other stage, and the sub-multiple frequency is taken from the Y output. For longer words, see typical application data, Figure 1.

The unity/cascade input, when connected to the clock input, may be utilized to pass the clock frequency (inverted) to the Y output when the rate input/decoding gates are inhibited by the strobe. The unity/cascade input may also be used as a control for the Y output.

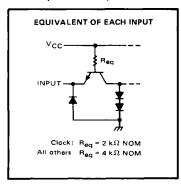

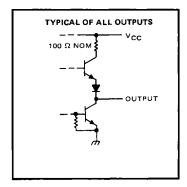

All of the Inputs of these counters are diode-clamped, and each input, except the clock input, represents one normalized Series 54/74 load. The buffered clock input, used with the strobe gate, is only two Series 54/74 loads. Full fan-out to 10 Series 54/74 loads is available from each of the output. These devices are completely compatible with most TTL and DTL families. Typical dissipation is 270 milliwatts. The SN54167 is characterized for operation over the full military temperature range of  $-55\,^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ , and the SN74167 is characterized for operation from 0°C to 70°C.

PRODUCTION DATA documents contain information current as of publication data. Products conform to specifications per the terms of Texas Instruments standerd warranty. Production processing does not necessarily include testing of all perameters.

2-537

#### STATE AND/OR RATE FUNCTION TABLE (See Note A)

| INPUTS |        |          |            |       |      |          |              |         |   | OUTPUTS |                      |       |  |  |  |

|--------|--------|----------|------------|-------|------|----------|--------------|---------|---|---------|----------------------|-------|--|--|--|

|        |        |          |            | BCD I | RATI | <u> </u> | NUMBER OF    | UNITY/  | - |         | EVEL OR<br>OF PULSES |       |  |  |  |

| CLEAR  | ENABLE | STROBE   | <b>B</b> 3 | B2    | В1   | 80       | CLOCK PULSES | CASCADE | Y | z       | ENABLE               | NOTES |  |  |  |

| н      | ×      | Н        | х          | Х     | Х    | х        | х            | н       | L | I       | Н                    | В     |  |  |  |

| L      | L      | Ł        | L          | L     | L    | L        | 10           | н       | L | H       | 1                    | С     |  |  |  |

| L      | L      | L        | Ł          | L     | L    | н        | 10           | н       | 1 | 1       | 1                    | c     |  |  |  |

| L      | L      | L        | L          | L     | н    | L        | 10           | н       | 2 | 2       | 1                    | c     |  |  |  |

| L      | L      | Ł        | L          | L     | н    | н        | 10           | н       | 3 | 3       | 1                    | c     |  |  |  |

| L      | L      | Ļ        | L          | Н     | L    | L        | 10           | н       | 4 | 4       | 1 1                  | С     |  |  |  |

| L      | L      | L        | L          | н     | L    | н        | 10           | н       | 5 | 5       | 1                    | C     |  |  |  |

| L      | L      | L        | L          | н     | н    | L        | 10           | н       | 6 | 6       | 1 1                  | C     |  |  |  |

| L      | L      | L        | L          | н     | н    | н        | 10           | н       | 7 | 7       | 1                    | C     |  |  |  |

| L      | L      | <u> </u> | Н          | L     | L    | L        | 10           | н       | 8 | 8       | 1                    | c     |  |  |  |

| L      | L      | L        | н          | L     | L    | Н        | 10           | н       | 9 | 9       | 1                    | С     |  |  |  |

| L      | L      | L        | H          | L     | н    | L        | 10           | н       | 8 | 8       | 1                    | C, D  |  |  |  |

| L      | L      | L        | н          | L     | н    | Н        | 10           | н       | 9 | 9       | 1                    | C, D  |  |  |  |

| L      | L      | L        | н          | н     | L    | L        | 10           | н       | 8 | 8       | 1                    | C, D  |  |  |  |

| L      | L      | L        | н          | н     | L    | Н        | 10           | H       | 9 | 9       | 1                    | C, D  |  |  |  |

| L      | L      | L        | н          | Н     | Н    | L        | 10           | н       | 8 | 8       | ,                    | C, D  |  |  |  |

| L      | L      | L        | н          | Н     | Н    | н        | 10           | Н       | 9 | 9       | 11                   | C, D  |  |  |  |

| L      | ٦      | L        | Н          | L     | L    | Н        | 10           | L       | Н | 9       | 1                    | Ε     |  |  |  |

- NOTES A. H = high level, L = low level, X = irrelevant. All remaining entries are numeric counts.

- B. This is a simplified illustration of the clear function. The states of clock and strobe can affect the logic level of Y and Z. A low unity/cascade will cause output Y to remain high.

- C Each rate illustrated assumes a constant value at rate inputs, however, these illustrations in no way prohibit variable rate inputs.

- D. These input conditions exceed the range of the decimal rate inputs.

- E. Unity/cascade can be used to inhibit output Y.

#### schematics of inputs and outputs

logic diagram (positive logic)

Texas VI POST OFFICE BOX 655012 . DALLAS TEXAS 75265

2-539

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1) |         |  |  |  |  |  |  |  |  |  |  |    |     |      | 7    | ' V |

|----------------------------------------------|---------|--|--|--|--|--|--|--|--|--|--|----|-----|------|------|-----|

| Input voltage                                |         |  |  |  |  |  |  |  |  |  |  |    |     |      | 5.5  | V   |

| Operating free-air temperature range:        | SN54167 |  |  |  |  |  |  |  |  |  |  | -5 | 5°( | C to | 125  | °C  |

|                                              | SN74167 |  |  |  |  |  |  |  |  |  |  |    | 0   | °C t | o 70 | °C  |

| Storage temperature range                    |         |  |  |  |  |  |  |  |  |  |  | _6 | 5°4 | ^ to | 150  | °C  |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                                                        |        | SN54167 |                     |      | SN74167 |                     |      |  |

|--------------------------------------------------------|--------|---------|---------------------|------|---------|---------------------|------|--|

|                                                        | MIN    | NON     | MAX                 | MIN  | NOM     | MAX                 | UNIT |  |

| Supply voltage, V <sub>CC</sub>                        | 4.5    | 5       | 5.5                 | 4.75 | 5       | 5.25                | ٧    |  |

| High-level output current, IOH                         |        |         | 400                 |      |         | -400                | μΑ   |  |

| Low-level output current, IOL                          |        |         | 16                  |      |         | 16                  | mΑ   |  |

| Clock frequency, f <sub>clock</sub>                    | O      |         | 25                  | 0    |         | 25                  | MHz  |  |

| Width of clock pulse, tw(clock)                        | 20     | )       |                     | 20   |         |                     | ns   |  |

| Width of clear pulse, tw(clear)                        | 15     |         |                     | 15   |         |                     | ns   |  |

| Width of set-to-nine pulse tw(set-to-9)                | 15     | ,       |                     | 15   |         |                     | ns   |  |

| Enable setup time, t <sub>su</sub> (See No             | te 21  |         |                     |      |         |                     |      |  |

| From positive-going transition of clock pulse          | 25     | i       |                     | 25   |         |                     | ns   |  |

| From negative-going transition of previous clock pulse | 0      | )       | tw(clock)-10        | 0    |         | tw(clock)-10        | ns   |  |

| Enable hold time, th: (See No                          | ote 2) |         |                     |      |         | -                   |      |  |

| From positive-going transition of clock pulse          | 0      | )       | tw(clock)-10        | 0    |         | tw(clock)-10        | ns   |  |

| From negative-going transition of previous clock pulse | 20     | )       | t <sub>cp</sub> -10 | 20   |         | t <sub>cp</sub> -10 | ns   |  |

| Operating free-air temperature, TA                     | -55    | i       | 125                 | 0    |         | 70                  | °C   |  |

NOTE 2: tw(clock) is the interval in which the clock is high. t<sub>cp</sub> is the total clock cycle starting with a negative transition. See Figure 1 on SN5497, SN7497 data sheet.

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                              |              | TEST CO                                            | ONDITIONS†                                          | MIN | TYP‡ | MAX                                 | UNIT |

|-----------------|----------------------------------------|--------------|----------------------------------------------------|-----------------------------------------------------|-----|------|-------------------------------------|------|

| VIH             | High-level input voltage               | _            |                                                    |                                                     | 2   |      |                                     | V    |

| VIL             | Low-level input voltage                |              |                                                    |                                                     |     |      | 0.8                                 | V    |

| VΙ              | Input clamp voltage                    |              | V <sub>CC</sub> = MIN,                             | I <sub>I</sub> = -12 mA                             |     |      | -1.5                                | V    |

| v <sub>OH</sub> | High-level output voltage              | –            | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -400 μA | 2.4 | 3.4  |                                     | ٧    |

| VOL             | Low-level output voltage               |              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 16 mA   |     | 0.2  | 0.4                                 | v    |

| l <sub>l</sub>  | Input current at maximum input voltage |              | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                              |     |      | 1                                   | mA   |

| 1               | High-level input current               | clock input  | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.4 V                              |     |      | 80                                  |      |

| ΊΗ              | riigii-level ilipat carrent            | other inputs | 7 * CC - MA^,                                      | V  ~ 2.4 V                                          |     |      | 40                                  | μΑ   |

| 1               | Low-level input current                | clock inputs | V <sub>CC</sub> = MAX,                             | Vı = 0.4 V                                          |     |      | -3.2                                | ^    |

| 11L             | Low-level input current                | other inputs | 7 °CC - MA^,                                       | V  - 0.4 V                                          |     |      | 0.8<br>-1.5<br>0.4<br>1<br>80<br>40 | mA   |

| los             | Short circuit output current §         |              | V <sub>CC</sub> = MAX                              |                                                     | -18 |      | -55                                 | mA   |

| Іссн            | Supply current, output high            |              | VCC = MAX,                                         | See Note 3                                          |     | 43   |                                     | mA   |

| ICCL            | Supply current, output low             |              | VCC = MAX,                                         | See Note 4                                          |     | 65   | 99                                  | mA   |

NOTES: 3.  ${}^{1}CCH$  is measured with outputs open and all inputs low.

$<sup>\</sup>S$  Not more than one output should be shorted at a time.

<sup>4.</sup> I CCL is measured with outputs open and all inputs high except the set to nine input which is low.

\*For test conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable.

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

#### SN54167, SN74167 SYNCHRONOUS DECADE RATE MULTIPLIERS

#### switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETERS T     | FROM<br>INPUT     | TO<br>OUTPUT | TEST CONDITIONS         | MIN | TYP | MAX | דומט |

|------------------|-------------------|--------------|-------------------------|-----|-----|-----|------|

| f <sub>max</sub> |                   |              |                         | 25  | 32  |     | MHz  |

| <sup>†</sup> PLH | Enable            | Enable       | 7                       |     | 13  | 20  |      |

| <sup>t</sup> PHL | - Chable          | Enable       |                         |     | 14  | 21  | ns   |

| <sup>t</sup> PLH | Strobe            | z            |                         |     | 12  | 18  |      |

| <sup>t</sup> PHL | Strobe            | 2            |                         |     | 15  | 23  | ns   |

| tPLH             | Clock             | Y            |                         |     | 26  | 39  |      |

| tPHL             |                   | •            |                         |     | 20  | 30  | пş   |

| <sup>t</sup> PLH | Clock             | z            | 7                       | -   | 12  | 18  |      |

| tPHL .           | CIOCK             | 2            |                         |     | 17  | 26  | ns   |

| <sup>t</sup> PLH | Rate              | z            | ] , ,,,,                |     | 9   | 14  |      |

| tPHL.            | nate              | 2            | C <sub>L</sub> = 15 pF, |     | 6   | 10  | ns   |

| <sup>t</sup> PLH | Unity/Cascade     | Y            | FiL ≈ 400 Ω,            |     | 9   | 14  |      |

| <sup>t</sup> PHL | Omity/Cascade     | ,            | See Note 5              |     | 6   | 10  | ns   |

| <sup>t</sup> PLH | Strobe            | Y            | 7                       |     | 19  | 30  |      |

| <sup>t</sup> PHL | Strobe            | •            |                         |     | 22  | 33  | ns   |

| <sup>t</sup> PLH | Clock             | Enable       |                         |     | 19  | 30  |      |

| tPHL .           | Olock             | Livable      |                         |     | 22  | 33  | ns   |

| ФLН              | Clear             | Y            |                         |     | 24  | 36  | Ī    |

| <sup>t</sup> PHL | PHL Z             |              |                         |     | 15  | 23  | ns   |

| <sup>t</sup> PHL | Set-to-9 Enable   |              |                         |     | 18  | 27  | ns   |

| <sup>t</sup> PLH | Any Rate Input    | Y            | 7                       |     | 15  | 23  |      |

| tPHL .           | ] Silv Hate Hipat | •            |                         |     | 15  | 23  | ns   |

<sup>†</sup>f<sub>max</sub> is maximum clock frequency.

TTL Devices N

than is maximal clock requency.

tp\_H is propagation delay time, low-to-high-level output.

tp\_H is propagation delay time, high-to-low-level output

NOTE 5: Load circuit, voltage waveforms, and input conditions for measuring switching characteristics are the same as those for the SN5497 and SN7497.

#### TYPICAL APPLICATION DATA

2-542