## PART NUMBER 9310DMC-ROCV

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

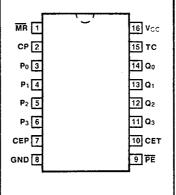

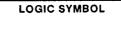

CONNECTION DIAGRAM

PINOUT A

9310 • 9316

93L10 • 93L16

93\$10 • 93\$16

### **BCD DECADE COUNTER/** 4-BIT BINARY COUNTER

**DESCRIPTION** — The '10 is a high speed synchronous BCD decade counter and the '16 is a high speed synchronous 4-bit binary counter. They are synchronously presetable, multifunctional MSI building blocks useful in a large number of counting, digital integration and conversion applications. Several states of synchronous operation are obtainable with no external gating packages required through an internal carry lookahead counting technique.

- SYNCHRONOUS COUNTING AND PARALLEL ENTRY

- DECODED TERMINAL COUNT

- BUILT-IN CARRY CIRCUITRY

- EASY INTERFACING WITH DTL, LPDTL, AND TTL FAMILIES

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                           | MILITARY GRADE                                                                                        | PKG  |

|--------------------|-----|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|

| PKGS               | ОПТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{ C to } +70^{\circ}\text{ C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C} \text{ to } +125^{\circ}\text{ C}$ | TYPE |

| Plastic<br>DIP (P) | А   | 9310PC, 9316PC<br>93L10PC, 93L16PC<br>93S10PC, 93S16PC                                     |                                                                                                       | 9B   |

| Ceramic<br>DIP (D) | А   | 9310DC, 9316DC<br>93L10DC, 93L16DC<br>93S10DC, 93S16DC                                     | 9310DM, 9316DM<br>93L10DM, 93L16DM<br>93S10DM, 93S16DM                                                | 6B   |

| Flatpak<br>(F)     | А   | 9310FC, 9316FC<br>93L10FC, 93L16FC<br>93S10FC, 93S16FC                                     | 9310FM, 9316FM<br>93L10FM, 93L16FM<br>93S10FM, 93S16FM                                                | 4L   |

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                             | DESCRIPTION                                  | 93XX (U.L.)<br>HIGH/LOW | 93L (U.L.)<br>HIGH/LOW | 93S (U.L.)<br>HIGH/LOW |

|---------------------------------------|----------------------------------------------|-------------------------|------------------------|------------------------|

| CEP.                                  | Count Enable Parallel Input                  | 1.0/1.0                 | 0.5/0.25               | 2.5/2.5                |

| CET                                   | Count Enable Trickle Input                   | 2.0/2.0                 | 1.0/0.5                | 3.1/3.1                |

| CP                                    | Clock Pulse Input (Active Rising Edge)       | 2.0/2.0                 | 1.0/0.5                | 3.1/3.1                |

| MR                                    | Asynchronous Master Reset Input (Active LOW) | 1.0/1.0                 | 0.5/0.25               | 1.25/1.25              |

| P <sub>0</sub> — P <sub>3</sub>       | Parallel Data Inputs                         | 0.67/0.67               | 0.33/0.17              | 1.25/1.25              |

| P <sub>0</sub> — P <sub>3</sub><br>PE | Parallel Enable Input (Active LOW)           | 2.0/2.0                 | 1.0/0.5                | 2.5/2.5                |

| Q <sub>0</sub> Q <sub>3</sub>         | Flip-flop Outputs                            | 16/8.0                  | 10/5.0<br>(3.0)        | 20/10                  |

| тс                                    | Terminal Count Output                        | 20/10                   | 10/5.0<br>(3.0)        | 25/12.5                |

'16, 'L16

09310-2x 6-31

1523

D-06

10 • 16

NATIONAL SEMICOND {LOGIC} DZE D 6501122 0064126 0

6-32 09310-3X

1524 D-07

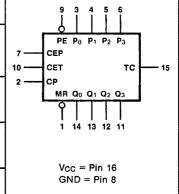

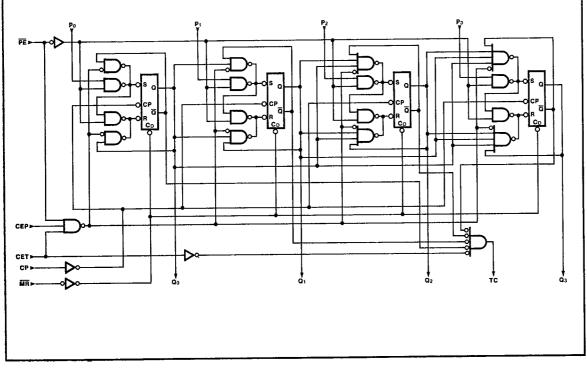

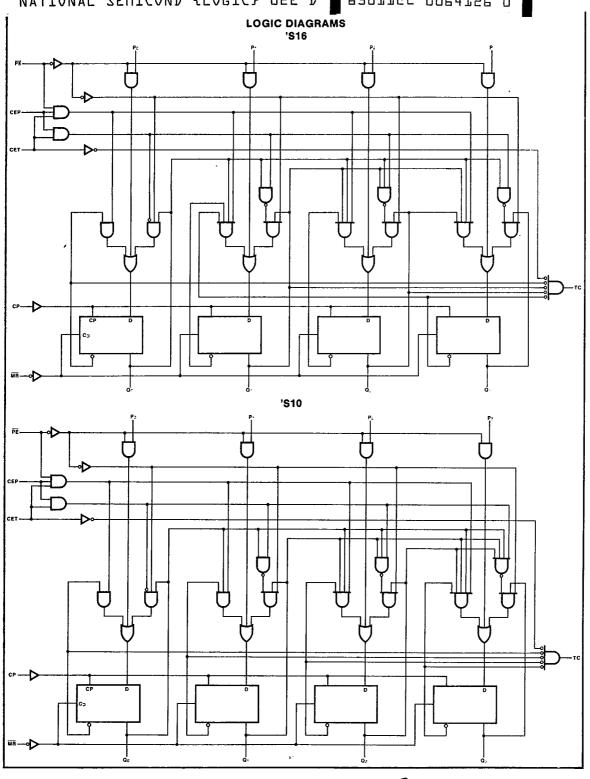

FUNCTIONAL DESCRIPTION — The '10 counts modulo-10 in the BCD (8421) sequence. From state 9 (HLLH) it increments to state 0 (LLLL). The '16 counts modulo-16 in binary sequence. From state 15 (HHHH) it increments to state 0 (LLLL). The clock inputs of all flip-flops are driven in parallel through a clock buffer. Thus all changes of the Q outputs (except due to Master Reset) occur as a result of, and synchronous with, the LOW-to-HIGH transition of the CP input signal. The circuits have four fundamental modes of operation, in order of precedence: asynchronous reset, parallel load, count-up and hold. Four control inputs — Master Reset (MR) Parallel Enable (PE), Count Enable Parallel (CEP) and Count Enable Trickle (CET) — determine the mode of operation, as shown in the Mode Select Table. A LOW signal on MR overrides all other inputs and asynchronously forces all outputs LOW. A LOW signal on PE overrides counting and allows information on the Parallel Data (Pn) inputs to be loaded into the flip-flops on the next rising edge of CP. With PE and MR HIGH, CEP and CET permit counting when both are HIGH. Conversely, a LOW signal on either CEP or CET inhibits counting.

The TTL and LP-TTL versions ('10, '16, 'L10 and 'L16 as opposed to the 'S10 and 'S16) contain masterslave flip-flops which are "next-state catching" because of the JK feedback. This means that when CP is LOW, information that would change the state of a flip-flop, whether from the counting logic or the parallel entry logic if either mode is momentarily enabled, enters the master and is locked in. Thus to avoid inadvertently changing the state of a master latch, and the subsequent transfer of the erroneous information to the slave when the clock rises, it is necessary to insure that neither the counting mode, nor the parallel entry mode is momentarily enabled while CP is LOW. The S-TTL versions ('S10 and 'S16) use D-type edge-triggered flip-flops and changing the PE, CEP and CET inputs when the CP is in either state does not cause errors, provided that the recommended setup and hold times, with respect to the rising edge of CP, are observed.

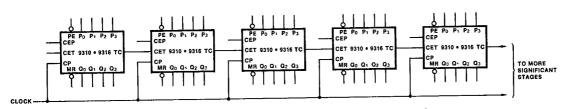

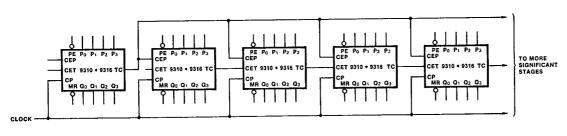

The Terminal Count (TC) output is HIGH when CET is HIGH and the counter is in its maximum count state (9 for the decade counters, 15 for the binary counters — fully decoded in both types). To implement synchronous multistage counters, the TC outputs can be used with the CEP and CET inputs in two different ways. These two schemes are shown in *Figures a and b*. The TC output is subject to decoding spikes due to internal race conditions and is therefore not recommended for use as a clock or asynchronous reset for flip-flops, counters or registers. If a decade counter is preset to an illegal state, or assumes an illegal state when power is applied, it will return to the normal sequence within two counts, as shown in the state diagrams.

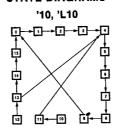

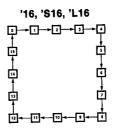

Multistage Counting — The '10/'16 counters may be cascaded to provide multistage synchronous counting. Two methods commonly used to cascade these counters are shown in *Figures a and b*.

In multistage counting, all less significant stages must be at their terminal count before the next more significant counter is enabled. The '10/'16 internally decodes the terminal count condition and "ANDs" it with the CET input to generate the terminal count (TC) output. This arrangement allows one to perform series enabling by connecting the TC output (enable signal) to the CET input of the following stage, Figure a. The setup requires very few interconnections, but has the following drawback: since it takes time for the enable to ripple through the counter stages, there is a reduction in maximum counting speed. To increase the counting rate, it is necessary to decrease the propagation delay of the TC signal, which is done in the second method.

The scheme illustrated in Figure b permits multistage counting, limited by the fan-out of the terminal count. The CEP input of the '10/'16 is internally "ANDed" with the CET input and as a result, both must be HIGH for the counter to be enabled. The CET inputs are connected as before except for the second stage. There the CET input is left floating and is therefore HIGH. Also, all CEP inputs are connected to the terminal output of the first stage. The advantage of this method is best seen by assuming all stages except the second and last are in their terminal condition. As the second stage advances to its terminal count, an enable is allowed to trickle down to the last counter stage, but has the full cycle time of the first counter to reach it. Then as the TC of the first stage goes active (HIGH), all CEP inputs are activated, allowing all stages to count on the next clock.

6

NATIONAL SEMICOND (LOGIC) DZE D 6501122 DD64128 3

#### MODE SELECT TABLE

|       |                  | INPUT                 | s                     |                       | RESPONSE                                                                                           |  |  |  |  |  |

|-------|------------------|-----------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MR    | ΡĒ               | CEP                   | CET                   | СР                    |                                                                                                    |  |  |  |  |  |

| LHIHH | X<br>L<br>H<br>H | X<br>X<br>L<br>X<br>H | X<br>X<br>X<br>L<br>H | \<br>x<br>\<br>x<br>\ | Clear; All Outputs LOW Parallel Load; P <sub>n</sub> → Q <sub>n</sub> Hold Hold; TC = LOW Count Up |  |  |  |  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = immaterial

#### **LOGIC EQUATIONS**

Count Enable = MR • PE • CEP • CET

Terminal Count = CET • Q<sub>0</sub> • Q<sub>1</sub> • Q<sub>2</sub> • Q<sub>3</sub> ('16)

Terminal Count = CET • Q<sub>0</sub> •  $\overline{Q}_1$  •  $\overline{Q}_2$  • Q<sub>3</sub> ('10)

#### STATE DIAGRAMS

NOTE: The '20 can be preset to any state, but will not count beyond 9. If preset to state 10,11,12,13,14 or 15, it will return to its normal sequence within two clock pulses.

Fig. a Synchronous Multistage Counting Scheme (Slow)

Fig. b Synchronous Multistage Counting Scheme (Fast)

| SYMBOL | PARAMETER                    | 93XX |     | 93L  |             | 935 |      | UNITS | CONDITIONS                         |

|--------|------------------------------|------|-----|------|-------------|-----|------|-------|------------------------------------|

|        | FARMILLER                    | Min  | Max | Min  | Max         | Min | Max  |       |                                    |

| los    | Output Short Circuit Current | -20  | -80 | -2.5 | <b>-</b> 25 | -40 | -100 | mA    | V <sub>CC</sub> = Max              |

| lcc    | Power Supply Current         |      | 92  |      | 27.5        |     | 127  | mA    | V <sub>CC</sub> = Max,<br>MR = Gnd |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25°C (See Section 3 for waveforms and load configurations)

|                  |                                | 93XX |                        | 93L |                        | 938 |           |       |                 |

|------------------|--------------------------------|------|------------------------|-----|------------------------|-----|-----------|-------|-----------------|

| SYMBOL           | PARAMETER                      | CL = | C <sub>L</sub> = 15 pF |     | C <sub>L</sub> = 15 pF |     | 15 pF     | UNITS | CONDITIONS      |

|                  |                                | Min  | Max                    | Min | Max                    | Min | Max       |       |                 |

| fmax             | Maximum Count Frequency        | 30   |                        | 13  |                        | 70  |           | MHz   |                 |

| tplH<br>tpHL     | Propagation Delay<br>CP to Q   |      | 20<br>23               |     | 32<br>39               |     | 9.0<br>13 | ns    | Figs. 3-1, 3-8  |

| tplH<br>tphL     | Propagation Delay<br>CP to TC  |      | 35<br>22               |     | 66<br>30               |     | 18<br>12  | ns    |                 |

| tPLH<br>tPHL     | Propagation Delay<br>CET to TC |      | 19<br>19               |     | 35<br>30               |     | 10<br>10  | ns    | Figs. 3-1, 3-5  |

| t <sub>PHL</sub> | Propagation Delay MR to Q      |      | 45                     |     | 62                     |     | 20        | ns    | Figs. 3-1, 3-16 |

C OPERATING REQUIREMENTS: VCC = +5.0 V, TA = +25° C

| SYMBOL                                   | DADAMETER                                  | 93XX           | 93L           | 938        | UNITS | CONDITIONS |

|------------------------------------------|--------------------------------------------|----------------|---------------|------------|-------|------------|

|                                          | PARAMETER                                  | Min Max        | Min Max       | Min Max    |       |            |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>Pn to CP         | 30<br>30       | 75<br>75      | 8.0<br>5.0 | ns    | Fig. 3-6   |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>Pn to CP          | 0<br>0         | 10<br>10      | 0<br>0     | ns    |            |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>PE to CP         | Note 2<br>30   | Note 2<br>53  | 10<br>5.0  | ns    | Fig. 3-6   |

| th (H)<br>th (L)                         | Hold Time HİGH or LOW<br>PE to CP          | -7.0<br>Note 2 | 7.0<br>Note 2 | 0<br>0     | ns    |            |

| ts (H)<br>ts (L)                         | Setup Time HIGH or LOW<br>CEP or CET to CP | 22<br>Note 1   | 26<br>Note 1  | 9.0<br>7.5 | ns    | Fig. 3-6 ^ |

| th (H)<br>th (L)                         | Hold Time HIGH or LOW<br>CEP or CET to CP  | Note 1<br>0    | Note 1<br>10  | 0          | ns    |            |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse Width                             | 17<br>17       | 25<br>25      | 6.5<br>7.0 | ns    | Fig. 3-8   |

| t <sub>w</sub> (L)                       | MR Pulse Width LOW                         | 30             | 65            | 14         | ns    | Fig. 3-16  |

| t <sub>rec</sub>                         | Recovery Time<br>MR to CP                  | 15             | 55            | 5.5        | ns    | Fig. 3-16  |

NOTES:

(1) The Setup Time "t<sub>6</sub> (L)" and Hold Time "t<sub>6</sub> (H)" between the Count Enable (CEP and CET) and the Clock (CP) indicate that the HIGH-to-LOW transition of the CEP and CET must occur only while the Clock is HIGH for conventional operation.

(2) The Setup Time "t<sub>6</sub> (H)" and Hold Time "t<sub>6</sub> (L)" between the Parallel Enable (PE) and Clock (CP) indicate that the LOW-to-HIGH transition of the PE must occur only while the Clock is HIGH for conventional operation.

09310-64 6-35

1527 0-10