## N-Bit 1 of 8 Decoder

The CDP1853 and CDP1853C are 1 of 8 decoders designed for use in general purpose microprocessor systems. These devices, which are functionally identical, are specifically designed for use as gated N-bit decoders and interface directly with the 1800-series microprocessors without additional components. The CDP1853 has a recommended operating voltage range of 4V to 10.5V, and the CDP1853C has a recommended operating voltage range of 4V to 6.5V.

When CHIP ENABLE (CE) is high, the selected output will be true (high) from the trailing edge of CLOCK A (high-to-low transition) to the trailing edge of CLOCK B (high-to-low transition). All outputs will be low when the device is not selected (CE = 0) and during conditions of CLOCK A and CLOCK B. The CDP1853 inputs N0, N1, N2, CLOCK A, and CLOCK B are connected to an 1800-series microprocessor outputs N0, N1, N2, TPA, and TPB respectively when used to decode I/O commands. The CHIP ENABLE (CE) input provides the capability for multiple levels of decoding.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

N-Bit 1 of 8 Decoder March 1997

#### Features

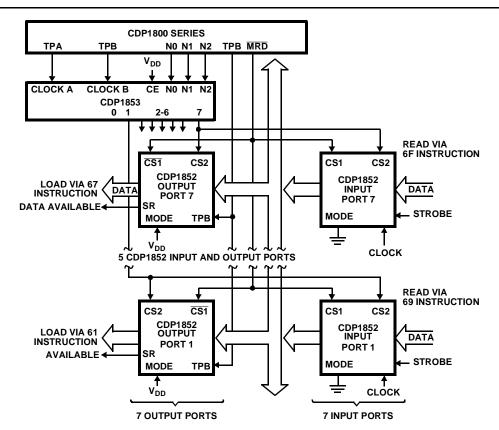

- Provides Direct Control of Up to 7 Input and 7 Output **Devices**

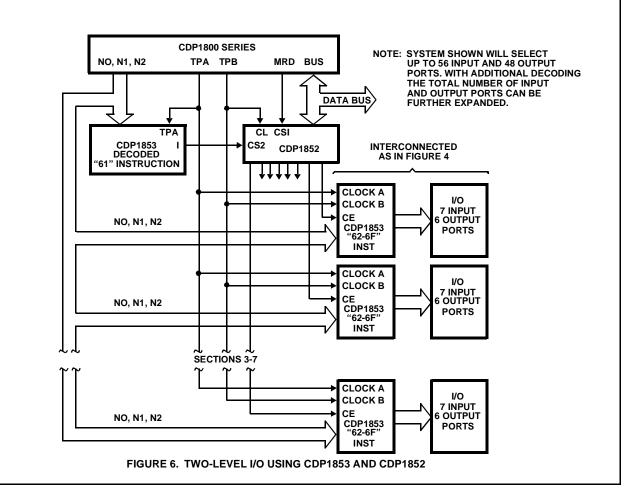

- . CHIP ENABLE (CE) Allows Easy Expansion for Multilevel I/O Systems

#### Ordering Information

| PACKAGE | TEMP. RANGE    | 5V         | 10V      | PKG.<br>NO. |

|---------|----------------|------------|----------|-------------|

| PDIP    | -40°C to +85°C | CDP1853CE  | CDP1853E | E16.3       |

| Burn-In |                | CDP1853CEX | -        | E16.3       |

| SBDIP   | -40°C to +85°C | CDP1853CD  | CDP1853D | D16.3       |

| Burn-In |                | CDP1853CDX | -        | D16.3       |

### Description

The CDP1853 and CDP1853C are 1 of 8 decoders designed for use in general purpose microprocessor systems. These devices, which are functionally identical, are specifically designed for use as gated N-bit decoders and interface directly with the 1800-series microprocessors without additional components. The CDP1853 has a recommended operating voltage range of 4V to 10.5V, and the CDP1853C has a recommended operating voltage range of 4V to 6.5V.

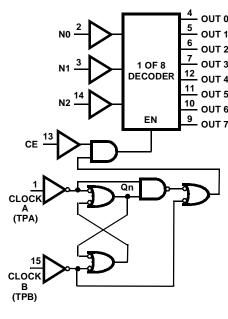

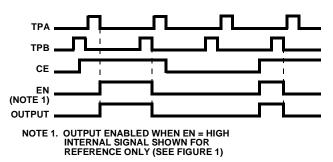

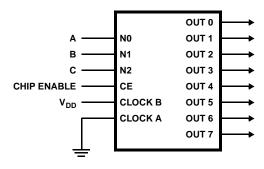

When CHIP ENABLE (CE) is high, the selected output will be true (high) from the trailing edge of CLOCK A (high-to-low transition) to the trailing edge of CLOCK B (high-to-low transition). All outputs will be low when the device is not selected (CE = 0) and during conditions of CLOCK A and CLOCK B as shown in Figure 2. The CDP1853 inputs N0, N1, N2, CLOCK A, and CLOCK B are connected to an 1800-series microprocessor outputs N0, N1, N2, TPA, and TPB respectively, when used to decode I/O commands as shown in Figure 5. The CHIP ENABLE (CE) input provides the capability for multiple levels of decoding as shown in Figure 6.

The CDP1853 can also be used as a general 1 of 8 decoder for I/O and memory system applications as shown in Figure 4.

The CDP1853 and CDP1853C are supplied in hermetic 16-lead dual-in-line ceramic (D suffix) and plastic (E suffix) packages.

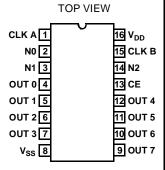

#### **Pinout** 16 LEAD DIP

## CDP1853 Functional Diagram

FIGURE 1.

#### TRUTH TABLE

| CE | CL A | CL B | EN    |

|----|------|------|-------|

| 1  | 0    | 0    | Qn-1† |

| 1  | 0    | 1    | 1     |

| 1  | 1    | 0    | 0     |

| 1  | 1    | 1    | 1     |

| 0  | X    | X    | 0     |

| N2    | N1       | N0      | EN    | 0    | 1  | 2   | 3    | 4    | 5  | 6 | 7 |

|-------|----------|---------|-------|------|----|-----|------|------|----|---|---|

| 0     | 0        | 0       | 1     | 1    | 0  | 0   | 0    | 0    | 0  | 0 | 0 |

| 0     | 0        | 1       | 1     | 0    | 1  | 0   | 0    | 0    | 0  | 0 | 0 |

| 0     | 1        | 0       | 1     | 0    | 0  | 1   | 0    | 0    | 0  | 0 | 0 |

| 0     | 1        | 1       | 1     | 0    | 0  | 0   | 1    | 0    | 0  | 0 | 0 |

| 1     | 0        | 0       | 1     | 0    | 0  | 0   | 0    | 1    | 0  | 0 | 0 |

| 1     | 0        | 1       | 1     | 0    | 0  | 0   | 0    | 0    | 1  | 0 | 0 |

| 1     | 1        | 0       | 1     | 0    | 0  | 0   | 0    | 0    | 0  | 1 | 0 |

| 1     | 1        | 1       | 1     | 0    | 0  | 0   | 0    | 0    | 0  | 0 | 1 |

| Χ     | Х        | Х       | 0     | 0    | 0  | 0   | 0    | 0    | 0  | 0 | 0 |

| 1 _ L | liah lov | /ol 0 – | LowLo | wol. | ν. | _ D | on't | - 00 | r0 |   |   |

1 = High level, 0 = Low level, X = Don't care † Qn-1 = Enable remains in previous state.

#### **Absolute Maximum Ratings**

####

#### **Thermal Information**

| Thermal Resistance (Typical)                   | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|------------------------------------------------|----------------------|----------------------|

| PDIP Package                                   | 85                   | N/A                  |

| SBDIP Package                                  |                      | 22                   |

| Operating Temperature Range (T <sub>A</sub> )  |                      |                      |

| Ceramic Packages (D Suffix Types)              |                      | 55°C to +125°C       |

| Plastic Packages (E Suffix Types)              |                      | 40°C to +85°C        |

| Storage Temperature Range (T <sub>STG</sub> )  |                      | -65°C to +150°C      |

| Lead Temperature (During Soldering)            |                      | +265°C               |

| At distance $1/16 \pm 1/32$ In. $(1.59 \pm 0)$ | .79mm)               |                      |

| from case for 10s max                          | ,                    |                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### Static Electrical Specifications At $T_A = -40$ to +85°C, Unless Otherwise Specified

|                                   |                  | cc                    | NDITION                | s                      | LIMITS           |                |     |       |                |     |       |

|-----------------------------------|------------------|-----------------------|------------------------|------------------------|------------------|----------------|-----|-------|----------------|-----|-------|

|                                   |                  |                       |                        |                        | CDP1853 CDP1853C |                |     |       |                |     |       |

| PARAMETER                         |                  | V <sub>o</sub><br>(V) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN              | (NOTE1)<br>TYP | MAX | MIN   | (NOTE1)<br>TYP | MAX | UNITS |

| Quiescent Device<br>Current       | Ι <sub>L</sub>   | -                     | -                      | 5                      | -                | 1              | 10  | -     | 5              | 50  | μΑ    |

| Current                           |                  | -                     | -                      | 10                     | -                | 10             | 100 | -     | -              | -   | μΑ    |

| Output Low Drive (Sink) Current   | I <sub>OL</sub>  | 0.4                   | 0, 5                   | 5                      | 1.6              | 3.2            | -   | 1.6   | 3.2            | -   | mA    |

| Current                           |                  | 0.5                   | 0, 10                  | 10                     | 2.6              | 5.2            | -   | -     | -              | -   | mA    |

| Output High Drive                 | I <sub>OH</sub>  | 4.6                   | 0, 5                   | 5                      | -1.15            | -2.3           | -   | -1.15 | -2.3           | -   | mA    |

| (Source) Current                  |                  | 9.5                   | 0, 10                  | 10                     | -2.6             | -5.2           | -   | -     | -              | -   | mA    |

| Output Voltage Low Level (Note 2) | V <sub>OL</sub>  | -                     | 0, 5                   | 5                      | -                | 0              | 0.1 | -     | 0              | 0.1 | V     |

| (Note 2)                          |                  | -                     | 0, 10                  | 10                     | -                | 0              | 0.1 | -     | -              | -   | V     |

| Output Voltage High Level         | V <sub>OH</sub>  | -                     | 0, 5                   | 5                      | 4.9              | 5              | -   | 4.9   | 5              | -   | V     |

|                                   |                  | -                     | 0, 10                  | 10                     | 9.9              | 10             | -   | -     | -              | -   | V     |

| Input Low Voltage                 | $V_{IL}$         | 0.5, 4.5              | -                      | 5                      | -                | -              | 1.5 | -     | -              | 1.5 | V     |

|                                   |                  | 1, 9                  | -                      | 10                     | -                | -              | 3   | -     | -              | -   | V     |

| Input High Voltage                | V <sub>IH</sub>  | 0.5, 4.5              | -                      | 5                      | 3.5              | -              | -   | 3.5   | -              | -   | V     |

|                                   |                  | 1, 9                  | -                      | 10                     | 7                | -              | -   | -     | -              | -   | V     |

| Input Leakage Current             | I <sub>IN</sub>  | Any                   | 0, 5                   | 5                      | -                | -              | ±1  | -     | -              | ±1  | μΑ    |

|                                   |                  | Input                 | 0, 10                  | 10                     | -                | -              | ±1  | -     | -              | -   | μΑ    |

| Operating Current                 | I <sub>DD1</sub> | 0, 5                  | 0, 5                   | 5                      | -                | 50             | 100 | -     | 50             | 100 | μΑ    |

| (Note 3)                          |                  | 0, 10                 | 0, 10                  | 10                     | -                | 150            | 300 | -     | -              | -   | μΑ    |

| Input Capacitance                 | C <sub>IN</sub>  | -                     | -                      | -                      | -                | 5              | 7.5 | -     | 5              | 7.5 | pF    |

| Output Capacitance                | C <sub>OUT</sub> | -                     | -                      | -                      | -                | 10             | 15  | -     | 10             | 15  | pF    |

#### NOTES:

- 1. Typical values are for  $T_A = +25^{\circ}C$  and nominal voltage.

- 2.  $I_{OL} = I_{OH} = 1\mu A$

- 3. Operating current measured in a CDP1802 system at 2MHz with outputs floating.

**Recommended Operating Conditions** At  $T_A$  = Full Package Temperature Range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

|                                 |                 | LIM             | IITS            |                 |       |

|---------------------------------|-----------------|-----------------|-----------------|-----------------|-------|

|                                 | CDP             | 1853            | CDP1            | 853C            |       |

| PARAMETER                       | MIN             | MAX             | MIN             | MAX             | UNITS |

| Supply Voltage Range            | 4               | 10.5            | 4               | 6.5             | V     |

| Recommended Input Voltage Range | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V     |

**Dynamic Electrical Specifications** At  $T_A = -40$  to  $+85^{\circ}$ C,  $V_{DD} = \pm 5\%$ ,  $V_{IH} = 0.7 V_{DD}$ ,  $V_{IL} = 0.3 V_{DD}$ ,  $t_R$ ,  $t_F = 20$ ns,  $C_L = 100$ pF, Unless Otherwise Specified

|                         |                    |                     |     |         | LIN | IITS |          |     |       |

|-------------------------|--------------------|---------------------|-----|---------|-----|------|----------|-----|-------|

|                         |                    |                     |     | CDP1853 |     |      | CDP1853C |     |       |

| PARAMETER               | _                  | V <sub>DD</sub> (V) | MIN | TYP     | MAX | MIN  | TYP      | MAX | UNITS |

| Propagation Delay Time: |                    |                     |     |         |     |      |          |     |       |

| CE to Output            | t <sub>EOH</sub> , | 5                   | -   | 175     | 275 | -    | 175      | 275 | ns    |

|                         | t <sub>EOL</sub>   | 10                  | -   | 90      | 150 | -    | -        | -   | ns    |

| N to Output             | t <sub>NOH</sub> , | 5                   | -   | 225     | 350 | -    | 225      | 350 | ns    |

|                         | t <sub>NOL</sub>   | 10                  | -   | 120     | 200 | -    | -        | -   | ns    |

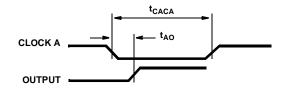

| Clock A to Output       | t <sub>AO</sub>    | 5                   | -   | 200     | 300 | -    | 200      | 300 | ns    |

|                         |                    | 10                  | -   | 100     | 150 | -    | -        | -   | ns    |

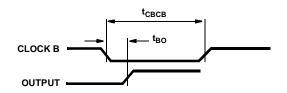

| Clock B to Output       | t <sub>BO</sub>    | 5                   | -   | 175     | 275 | -    | 175      | 275 | ns    |

|                         |                    | 10                  | -   | 90      | 150 | -    | -        | -   | ns    |

| Minimum Pulse Widths:   |                    |                     |     |         |     |      |          |     | ns    |

| Clock A                 | t <sub>CACA</sub>  | 5                   | -   | 50      | 75  | -    | 50       | 75  | ns    |

|                         |                    | 10                  | -   | 25      | 50  | -    | -        | -   | ns    |

| Clock B                 | t <sub>CBCB</sub>  | 5                   | -   | 50      | 75  | -    | 50       | 75  | ns    |

|                         |                    | 10                  | -   | 25      | 50  | -    | -        | -   | ns    |

#### NOTES:

- 1. Maximum limits of minimum characteristics are the values above which all devices function.

- 2. Typical values are for  $T_A = +25^{\circ}C$  and nominal voltages.

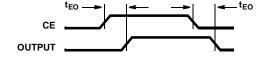

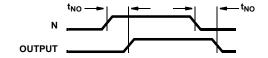

## **Timing Diagrams**

FIGURE 2A. CE TO OUTPUT (0-7) DELAY TIME

FIGURE 2B. N LINES TO OUTPUT (0-7) DELAY TIME

FIGURE 2C. CLOCK A TO OUTPUT (0-7) DELAY TIME

FIGURE 2D. CLOCK B TO OUTPUT (0-7) DELAY TIME

FIGURE 2. PROPAGATION DELAY TIME DIAGRAMS

FIGURE 3. TIMING DIAGRAM

FIGURE 4. N-BIT DECODER USED AS A 1 OF 8 DECODER

FIGURE 5. N-BIT DECODER IN A ONE-LEVEL I/O SYSTEM

| All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.  Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

For information regarding Intersil Corporation and its products, see www.intersil.com

## Sales Office Headquarters

#### NORTH AMERICA

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618

TEL: (949) 341-7000 FAX: (949) 341-7123

## Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905

TEL: (321) 724-7000 FAX: (321) 724-7946

#### **EUROPE**

Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland TEL: +41 21 6140560

FAX: +41 21 6140579

#### **ASIA**

Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433